Steward

分享是一種喜悅、更是一種幸福

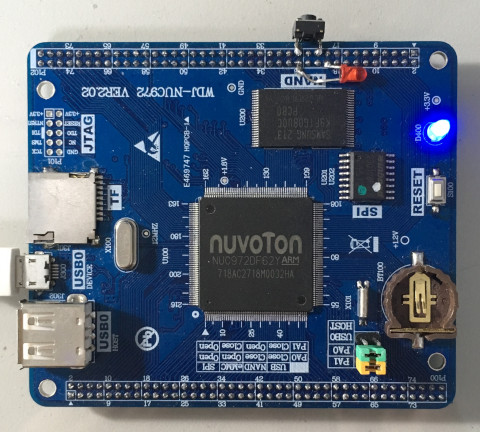

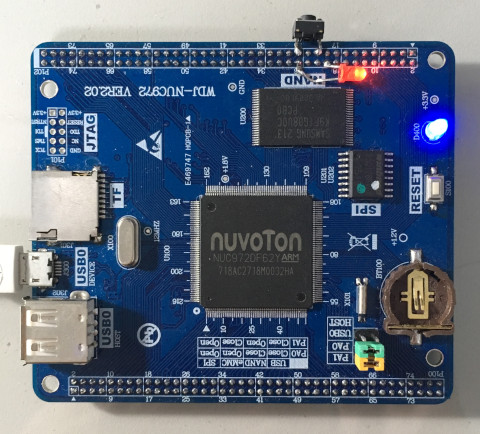

微處理器 - Nuvoton NUC972 - Assembly - Phase Locked Loop(PLL)

參考資訊:

https://github.com/OpenNuvoton/NUC970_NonOS_BSP

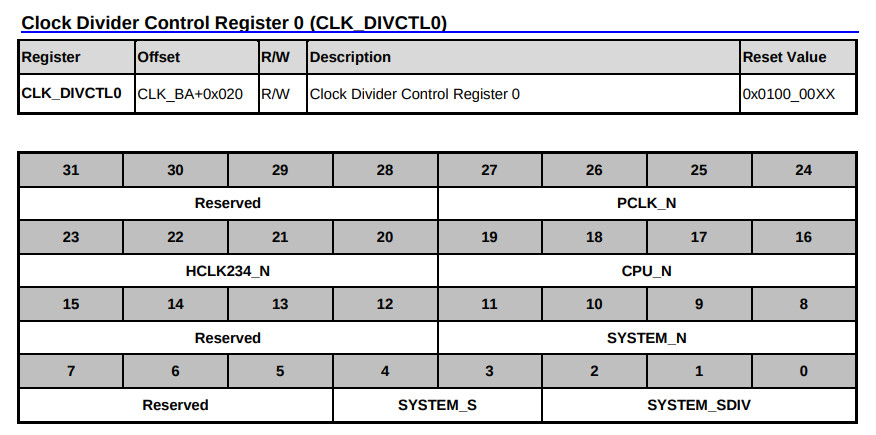

DIVCTL0

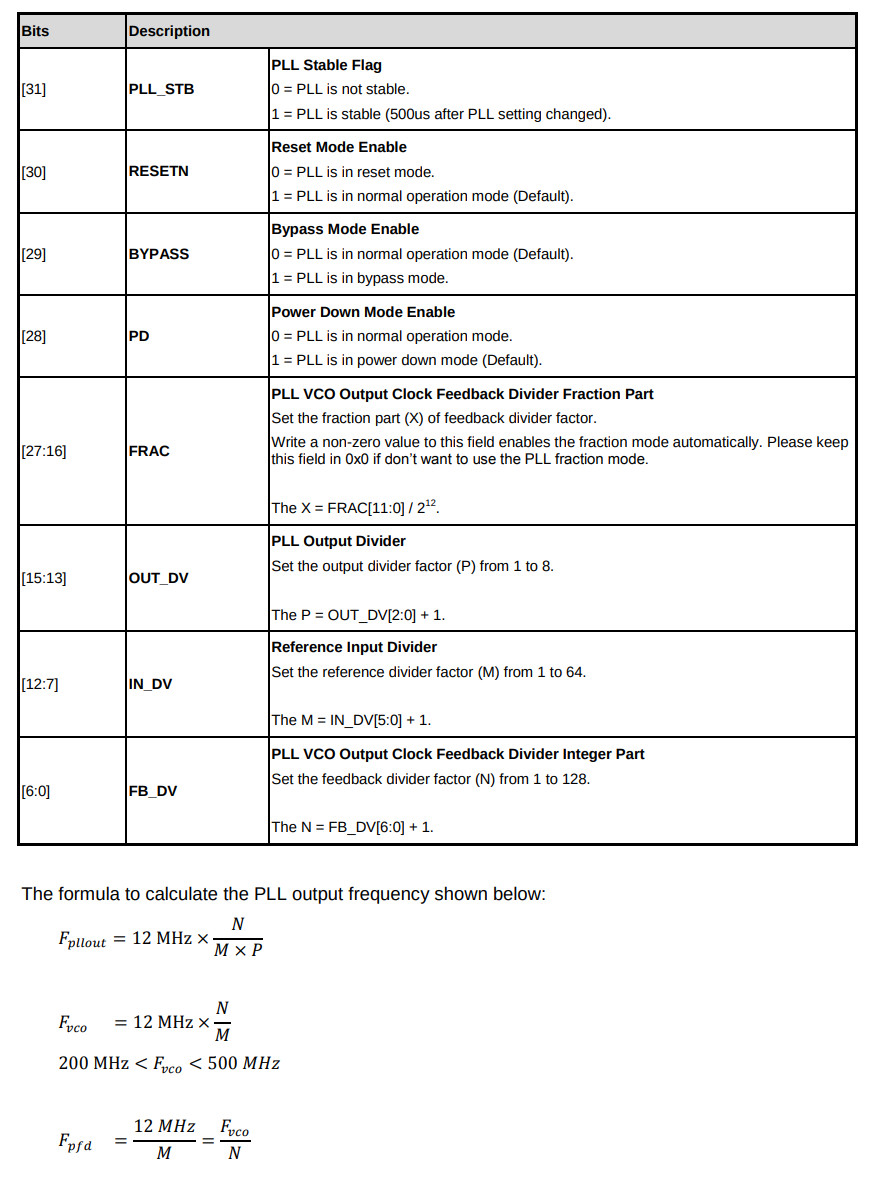

APLL、UPLL

PLL

main.s

.equ GPIOB_DIR, (0xb8003000 + 0x40)

.equ GPIOB_DATAOUT, (0xb8003000 + 0x44)

.equ CLK_PCLKEN0, (0xb0000200 + 0x18)

.equ CLK_DIVCTL0, (0xb0000200 + 0x20)

.equ CLK_APLLCON, (0xb0000200 + 0x60)

.equ CLK_UPLLCON, (0xb0000200 + 0x64)

.text

.align 2

.global _start

_start: b reset

_undef: b .

_swi: b .

_pabort: b .

_dabort: b .

_reserved: b .

_irq: b .

_fiq: b .

reset:

ldr r0, =CLK_UPLLCON

ldr r1, =0x4000001b

str r1, [r0]

ldr r0, =CLK_DIVCTL0

ldr r1, [r0]

and r1, #0xfff0ffff

str r1, [r0]

ldr r0, =CLK_PCLKEN0

ldr r1, [r0]

orr r1, #(1 << 3)

str r1, [r0]

ldr r0, =GPIOB_DIR

ldr r1, =(1 << 0)

str r1, [r0]

loop:

ldr r0, =GPIOB_DATAOUT

ldr r1, =(1 << 0)

str r1, [r0]

ldr r4, =1000000

1:

nop

subs r4, r4, #1

bne 1b

ldr r0, =GPIOB_DATAOUT

ldr r1, =~(1 << 0)

str r1, [r0]

ldr r4, =1000000

1:

nop

subs r4, r4, #1

bne 1b

b loop

.end

P.S. 除了詭異的SYS_PWRON、APLL、UPLL,還需要注意PA.2(1 = System clock is from UPLL output)腳位的設定,司徒目前PA.2是懸空,建議接到VCC,正確使用UPLL

完成