Steward

分享是一種喜悅、更是一種幸福

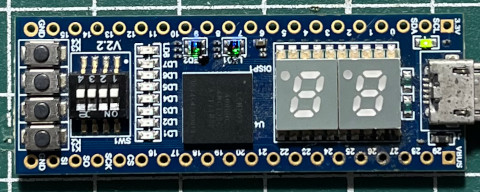

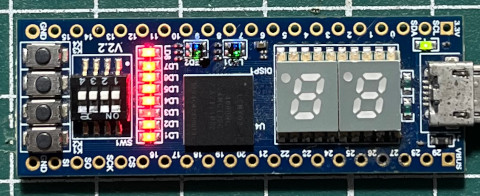

微處理器 - Lattice LCMXO2-4000HC-4MG132C (STEP-MXO2 V2) - Lattice Diamond - VHDL - LED

參考資訊:

https://www.stepfpga.com/doc/step-mxo2%E5%85%A5%E9%97%A8%E6%95%99%E7%A8%8B

main.vhd

library ieee;

use ieee.std_logic_1164.all;

entity main is

port(

clk : in std_logic;

led : out std_logic_vector(0 to 7) := "11111111"

);

end main;

architecture logic of main is

begin

process(clk) is

variable cnt : integer := 0;

variable val: std_logic_vector(0 to 7) := "11111111";

begin

if (clk'event and clk = '1') then

cnt := cnt + 1;

if (cnt = 1000000) then

cnt := 0;

led <= val;

val := not val;

end if;

end if;

end process;

end logic;

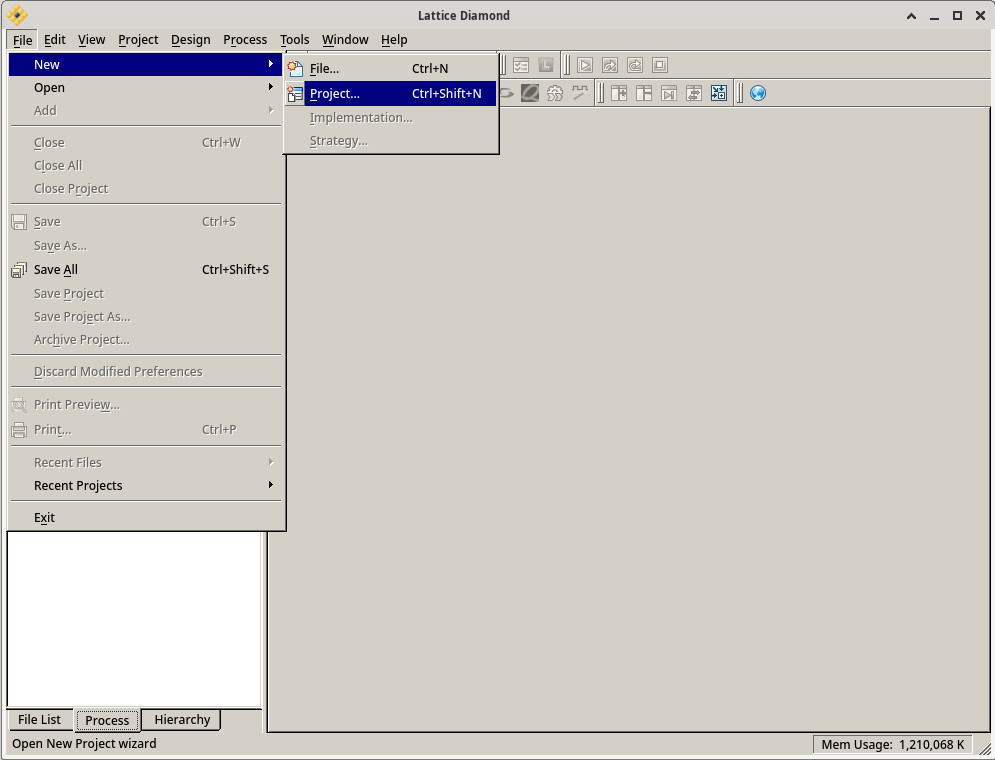

New => Project

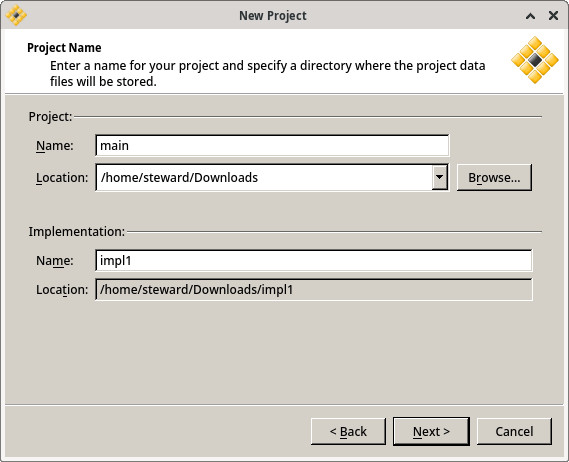

Name

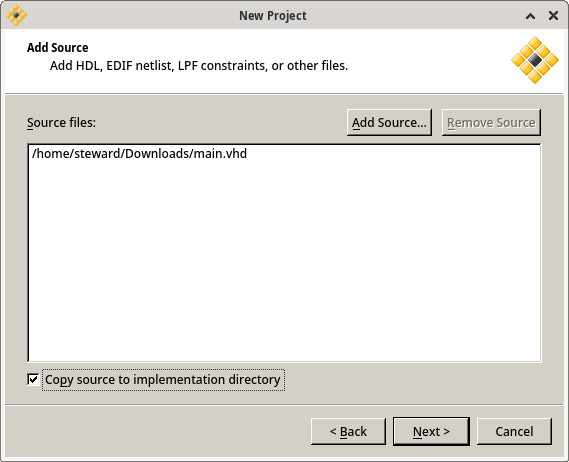

加入main.vhd

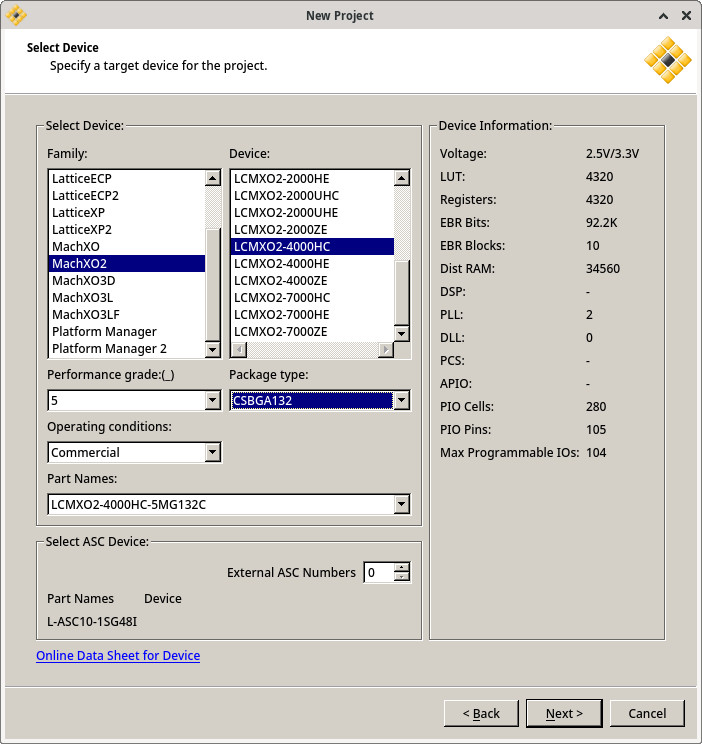

選擇型號

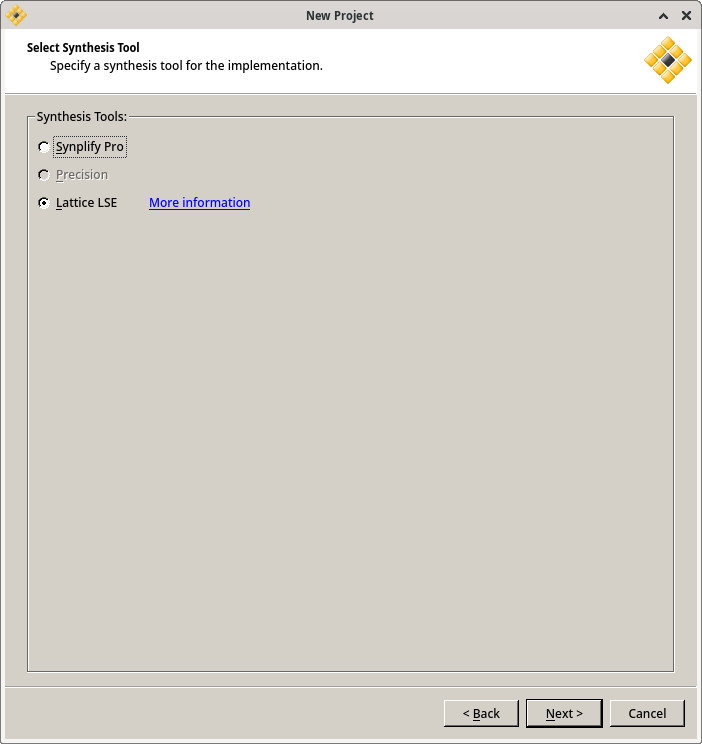

Lattice LSE

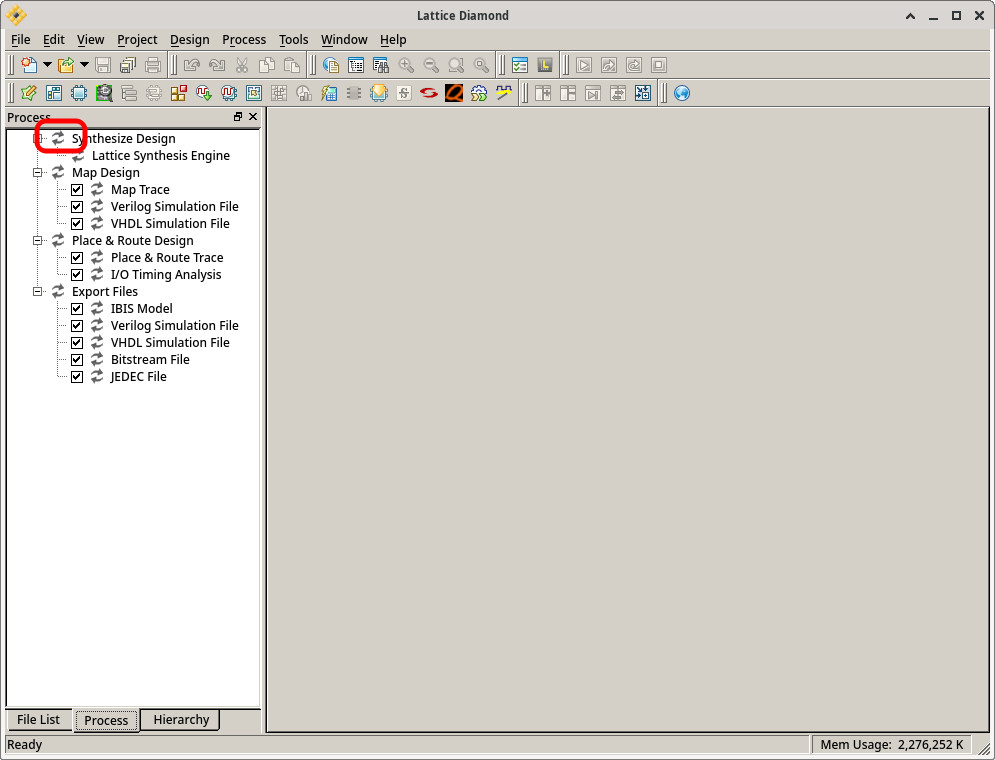

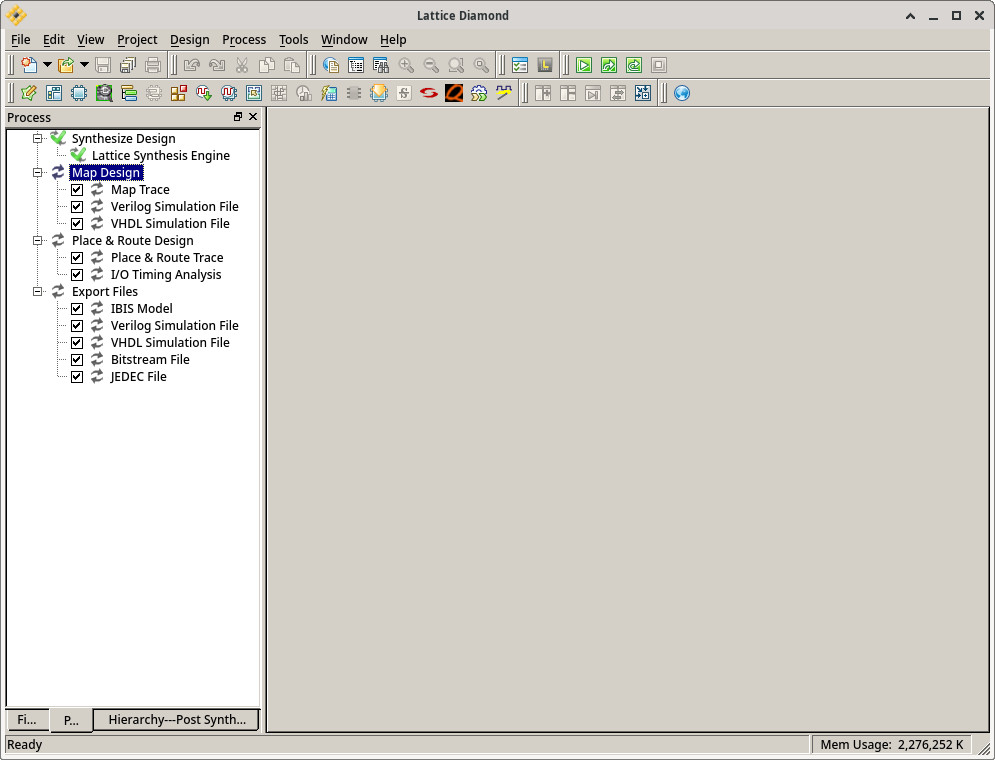

用滑鼠Double Click箭頭部份

完成合成

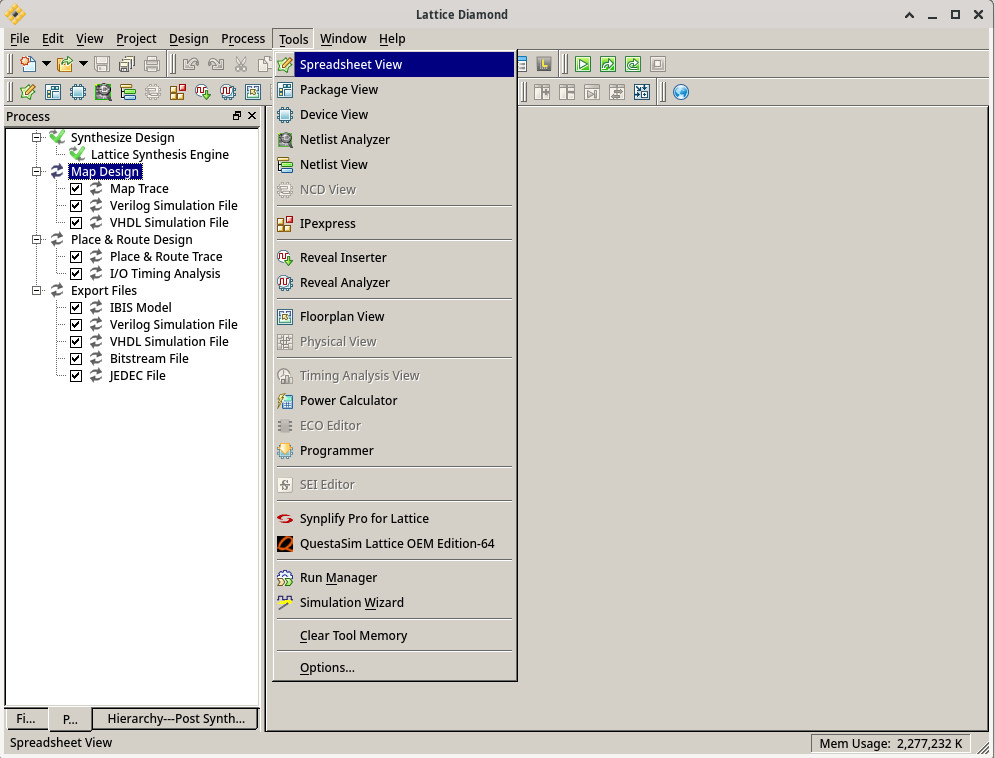

Tools => Spreadsheet View

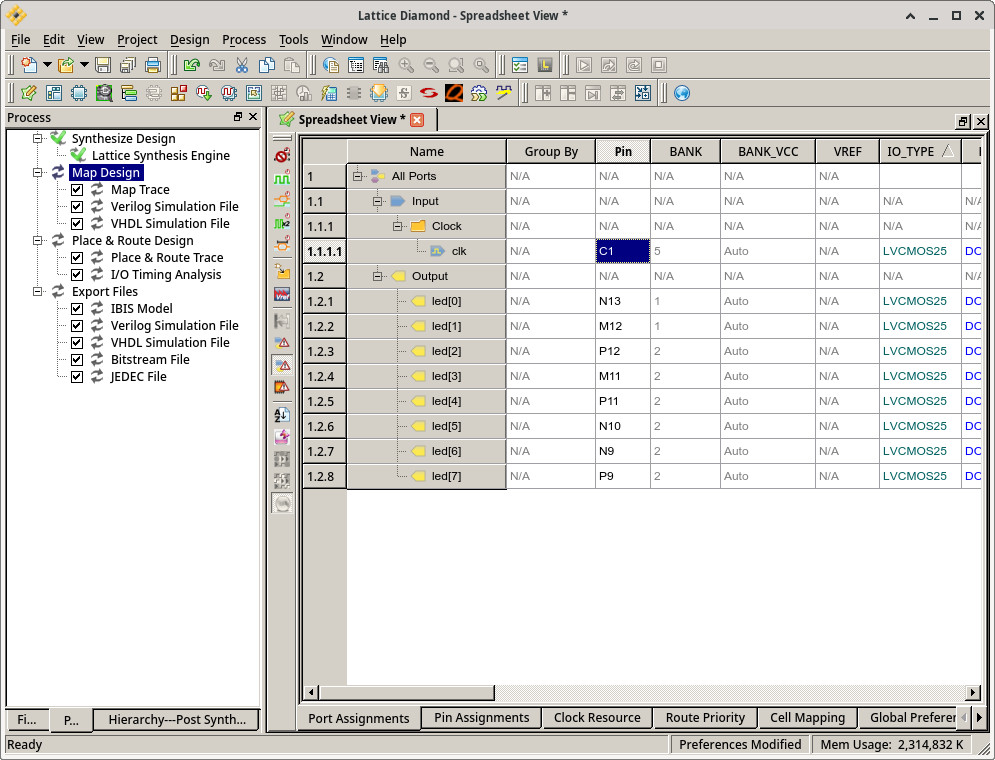

編輯腳位

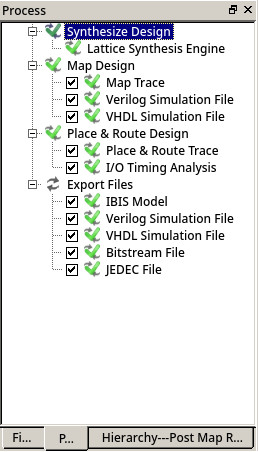

用滑鼠Double Click其餘部份,讓全部變成綠色狀態

燒錄

$ openFPGALoader -m -d /dev/ttyUSB0 main_impl1.jed

empty

write to ram

No cable or board specified: using direct ft2232 interface

Can't read iSerialNumber field from FTDI: considered as empty string

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Open file DONE

Parse file DONE

Enable configuration: DONE

SRAM erase: DONE

Enable configuration: DONE

Flash erase: DONE

Writing data: [==================================================] 100.00%

Done

Write program Done: DONE

Disable configuration: DONE

完成