Steward

分享是一種喜悅、更是一種幸福

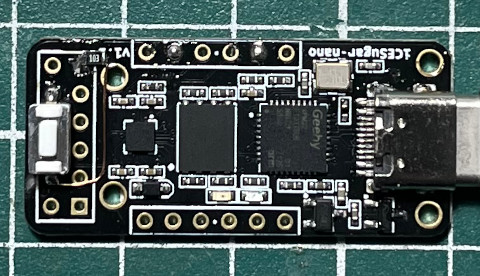

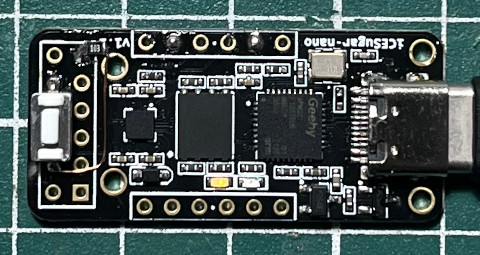

微處理器 - Lattice iCE40LP1K-CM36 (iCESugar-nano) - VHDL - LED

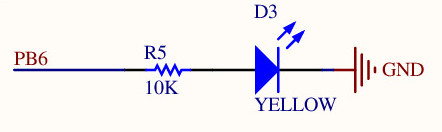

LED腳位

main.vhd

library ieee;

use ieee.std_logic_1164.all;

entity main is

port(

clk : in std_logic;

led : out std_logic

);

end main;

architecture logic of main is

begin

process(clk) is

variable cnt : integer := 0;

variable val: std_logic := '0';

begin

if (clk'event and clk = '1') then

cnt := cnt + 1;

if (cnt = 1000000) then

cnt := 0;

led <= val;

val := not val;

end if;

end if;

end process;

end logic;

main.pcf

set_io led B6 set_io clk D1

Makefile

all: yosys -m ghdl -p "ghdl main.vhd -e main; synth_ice40 -json main.json -blif main.blif" nextpnr-ice40 --lp1k --package cm36 --json main.json --pcf main.pcf --asc main.asc --freq 48 icepack main.asc main.bin run: icesprog -w main.bin clean: rm -rf main.blif main.asc main.bin main.json

編譯、燒錄

$ make $ make run

完成