Steward

分享是一種喜悅、更是一種幸福

掌機 - GP2X Wiz - Assembly - Timer3

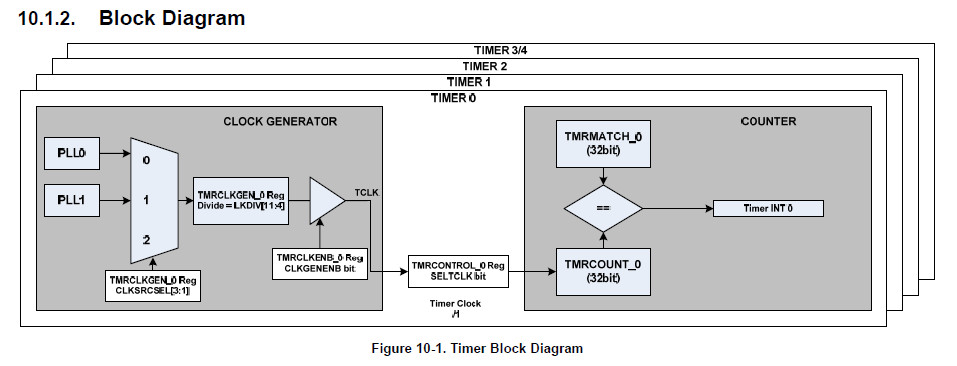

Timer架構

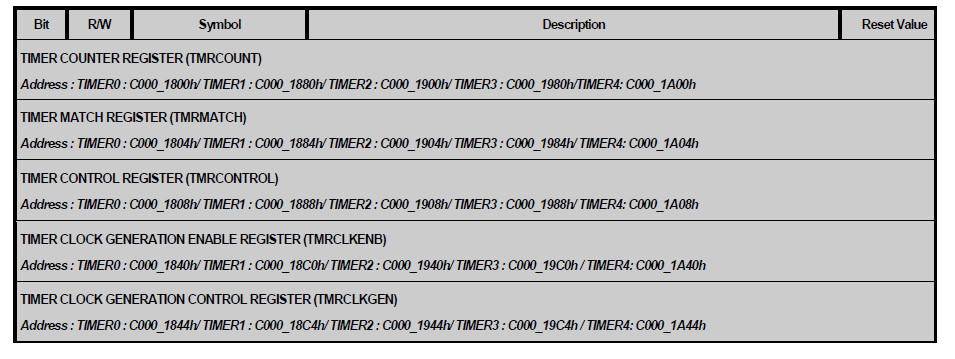

暫存器

Timer計數(使用UART開機模式時,Clock固定使用PLL1且速度為147.46MHz)

TCLK = (PLL1 / CLKDIV) / SELTCLK PLL1 = 147.46MHz CLKDIV = 40 SELTCLK = 2 TCLK = (147.46MHz / 40) / 2 = 1843250Hz

main.s

.global _start

.equiv GPIOC_OUT, 0xc000a080

.equiv GPIOC_OUTENB, 0xc000a084

.equiv INTMODEL, 0xc0000808

.equiv INTMASKL, 0xc0000810

.equiv INTPENDL, 0xc0000820

.equiv TMR3_COUNT, 0xc0001980

.equiv TMR3_MATCH, 0xc0001984

.equiv TMR3_CONTROL, 0xc0001988

.equiv TMR3_CLKENB, 0xc00019c0

.equiv TMR3_CLKGEN, 0xc00019c4

.arm

.text

_start:

b reset

b .

b .

b .

b .

b .

b irq_handler

b .

irq_handler:

ldr r0, =TMR3_CONTROL

ldr r1, [r0]

orr r1, #(1 << 5)

bic r1, #(1 << 3)

str r1, [r0]

ldr r0, =GPIOC_OUT

eor r2, #(1 << 16)

str r2, [r0]

ldr r0, =INTPENDL

ldr r1, =0xffffffff

str r1, [r0]

ldr r0, =TMR3_CONTROL

ldr r1, [r0]

orr r1, #(1 << 3)

str r1, [r0]

subs pc, lr, #4

reset:

mrs r0, cpsr

bic r0, #0x80

msr cpsr_c, r0

ldr r0, =INTMODEL

ldr r1, =0

str r1, [r0]

ldr r0, =INTMASKL

ldr r1, =0

str r1, [r0]

ldr r0, =INTPENDL

ldr r1, =0xffffffff

str r1, [r0]

ldr r0, =GPIOC_OUTENB

ldr r1, =(1 << 16)

str r1, [r0]

ldr r0, =GPIOC_OUT

ldr r2, =(1 << 16)

str r2, [r0]

ldr r0, =TMR3_CLKGEN

ldr r1, =(39 << 4) | (1 << 1)

str r1, [r0]

ldr r0, =TMR3_CLKENB

ldr r1, =0x0c

str r1, [r0]

ldr r0, =TMR3_COUNT

ldr r1, =0

str r1, [r0]

ldr r0, =TMR3_MATCH

ldr r1, =1843250

str r1, [r0]

ldr r0, =TMR3_CONTROL

ldr r1, =0x38

str r1, [r0]

b .

.end

完成