Canon wordtank Z900

如何使用JTAG Debug

參考資訊:

1. jlink

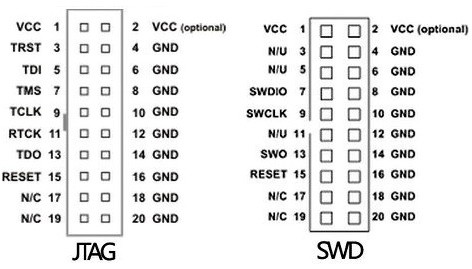

2. pinout

JTAG腳位

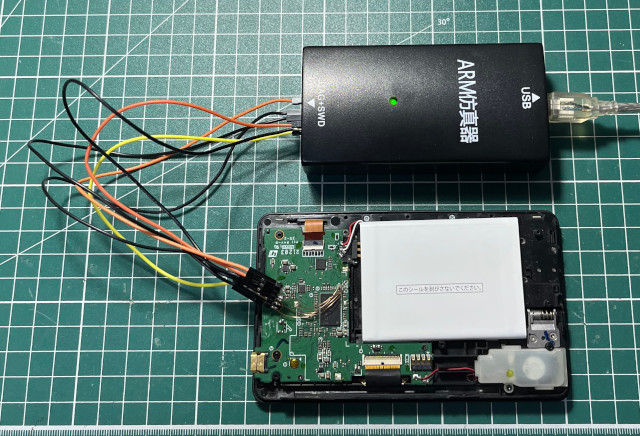

1. 將Z900連接到JTAG

2. 安裝JLink_Linux_x86_64.deb

3. Z900上電

4. Jtag Debug

$ JLinkExe

SEGGER J-Link Commander V7.90 (Compiled Aug 2 2023 15:24:10)

DLL version V7.90, compiled Aug 2 2023 15:23:50

Connecting to J-Link via USB...O.K.

Firmware: J-Link ARM V8 compiled Nov 28 2014 13:44:46

Hardware version: V8.00

J-Link uptime (since boot): N/A (Not supported by this model)

S/N: 788531798

License(s): RDI,FlashDL,FlashBP,JFlash,GDB

VTref=3.319V

Type "connect" to establish a target connection, '?' for help

J-Link>connect

Please specify device / core. <Default>: S3C44B0X

Type '?' for selection dialog

Device>

Please specify target interface:

J) JTAG (Default)

TIF>

Device position in JTAG chain (IRPre,DRPre) <Default>: -1,-1 => Auto-detect

JTAGConf>

Specify target interface speed [kHz]. <Default>: 4000 kHz

Speed>

Device "S3C44B0X" selected.

Connecting to target via JTAG

TotalIRLen = 4, IRPrint = 0x01

JTAG chain detection found 1 devices:

#0 Id: 0x079264F3, IRLen: 04, ARM926EJ-S Core

Identified core does not match configuration. (Found: ARM9, Configured: ARM7)

Using DBGRQ to halt CPU

CP15.0.0: 0x41069265: ARM, Architecture 5TEJ

CP15.0.1: 0x1D192152: ICache: 16kB (4*128*32), DCache: 32kB (4*256*32)

Cache type: Separate, Write-back, Format C (WT supported)

Memory zones:

Zone: "Default" Description: Default access mode

ARM9 identified.

ETM V3.2: 4 pairs addr.comp, 2 data comp, 0 MM decs, 2 counters, sequencer

J-Link>halt

Using DBGRQ to halt CPU

J-Link: ARM9 CP15 Settings changed: 5227B from 78, MMU On, ICache Off, DCache Off

PC: (R15) = 80209A90, CPSR = 60000093 (SVC mode, ARM IRQ dis.)

Current:

R0 =00000000, R1 =60000093, R2 =37CC30A5, R3 =37CC3A80

R4 =000009DB, R5 =81C0718C, R6 =81C0670C, R7 =00000000

R8 =00000001, R9 =00000000, R10=00000000, R11=D02CFC14, R12=80216EA8

R13=FFFFC78C, R14=80209184, SPSR=60000010

USR: R8 =00000001, R9 =00000000, R10=00000000, R11=D02CFC14, R12=80216EA8

R13=D02CFA14, R14=802319D0

FIQ: R8 =00000000, R9 =00000000, R10=00000000, R11=00000000, R12=00000000

R13=FFFF0900, R14=00000000, SPSR=00000010

IRQ: R13=FFFF0800, R14=FFFFC800, SPSR=00000013

SVC: R13=FFFFC78C, R14=80209184, SPSR=60000010

ABT: R13=FFFF1000, R14=F101FF98, SPSR=20000010

UND: R13=FFFFC800, R14=8021997C, SPSR=4000001F

J-Link>r

Reset delay: 0 ms

Reset type NORMAL: Using RESET pin, halting CPU after Reset

PC of target system has unexpected value of 0x80209C6C after reset.

CP15.0.0: 0x41069265: ARM, Architecture 5TEJ

CP15.0.1: 0x1D192152: ICache: 16kB (4*128*32), DCache: 32kB (4*256*32)

Cache type: Separate, Write-back, Format C (WT supported)

J-Link>step 10

802194A8: 0F 50 2D E9 PUSH {R0-R3,R12,LR}

FFFF0010: D8 F3 9F E5 LDR PC, [PC, #+0x3D8] ; 0xFFFF03F0

802194A4: 08 E0 4E E2 SUB LR, LR, #0x08

802194A8: 0F 50 2D E9 PUSH {R0-R3,R12,LR}

FFFF0010: D8 F3 9F E5 LDR PC, [PC, #+0x3D8] ; 0xFFFF03F0

802194A4: 08 E0 4E E2 SUB LR, LR, #0x08

802194A8: 0F 50 2D E9 PUSH {R0-R3,R12,LR}

FFFF0010: D8 F3 9F E5 LDR PC, [PC, #+0x3D8] ; 0xFFFF03F0

802194A4: 08 E0 4E E2 SUB LR, LR, #0x08

802194A8: 0F 50 2D E9 PUSH {R0-R3,R12,LR}