Steward

分享是一種喜悅、更是一種幸福

手機 - Gemini PDA 4G - 製作UART接線

參考資訊:

http://www.omegamoon.com/blog/index.php?entry=entry180626-210224

雖然Gemini PDA的PCB主板有UART的TX、RX的焊點,不過為了美美的外觀,司徒目前還是不敢改機,因此,只好使用另一種透過USB-C轉換成UART的模式,這種模式就是在開機時(preload執行時),假如偵測到左邊USB-C的VCC腳位為+3.3V時,會把左邊USB-C變成UART模式,但是不具備+3.3V供電功能(不過可以充電),如要恢復成原本USB-C功能,只能重新開機,接著司徒就說明一下製作的步驟

如下接線:

| USB | PL2303 |

|---|---|

| VCC | +5V |

| D- | RX |

| D+ | TX |

| GND | GND |

綁成美美的樣子

為了讓它可以變成UART模式,司徒使用PL2303的+5V

PL2303接PC,而另一端則接Gemini PDA左邊的USB-C接口

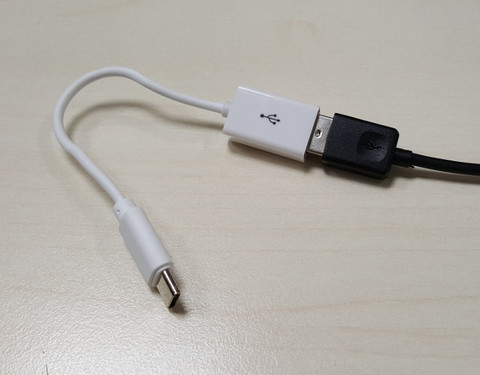

司徒使用USB-C轉接頭

記得先把PL2303接到PC,再接上Gemini PDA左邊USB-C接口,最後才可以打開Gemin PDA電源

P.S. Android下的UART位置為/dev/ttyMT0

Baudrate: 921600 bps

[PWRAP] pwrap_init_preloader [PWRAP] Preloader pwrap_init start!!!!!!!!!!!!! [PWRAP] Dump PD_CFG0=0x0 ([10]=MI,[11]=MO, [12]=CK, [13]=CSN), [PWRAP] Dump PU_CFG0=0x0 ([10]=MI,[11]=MO, [12]=CK, [13]=CSN), [PWRAP] SMT setting is OK.[PWRAP] DRV setting is OK.[PWRAP] slave IO setting is OK.[PWRAP] start reset wrapper [PWRAP] pwrap_init---- reset ok [PWRAP] spi clk set .... [PWRAP] pwrap_init---- clk set ok [PWRAP] pwrap_init---- dcm enable [PWRAP] pwrap_init---- slave reset ok [PWRAP] pwrap_init---- wacs2 enable ok [PWRAP] pwrap_init---- debug: init_reg_clock ok [PWRAP] pwrap_init---- debug: init_dio ok [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=0 rdata=4804 at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=1 rdata=E884 at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=2 rdata=E886 at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=3 rdata=E886 at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=8 rdata=2012 at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=9 rdata=A012 at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=10 rdata=A21A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=11 rdata=A21A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=12 rdata=A65A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=13 rdata=A65A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=14 rdata=A65A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=15 rdata=A65A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=16 rdata=804A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=17 rdata=804A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=18 rdata=886A at times=0 [PWRAP] _pwrap_init_sistrobe [Read Test of MT6351] tuning,index=19 rdata=886A at times=0 [PWRAP] _pwrap_init_sistrobe best point,at index=7 [PWRAP] pwrap_init---- strobe ok [PWRAP] mt_pwrap_init---- init_chiper1 [PWRAP] mt_pwrap_init---- init_chiper2 [PWRAP] mt_pwrap_init---- init_chiper3 [PWRAP] pwrap_init---- Cipher ok [PWRAP] pwrap_init---- adc_set ok [PWRAP] pwrap_init---- priority ok [PWRAP] pwrap_init---- wacs enable ok [PWRAP] Preloader PMIC_WRAP_WACS_P2P_EN=1 [PWRAP] Preloader PMIC_WRAP_INIT_DONE_P2P=1 [PWRAP] Preloader pwrap_init Done!!!!!!!!! [PWRAP] after MT6351 pwrap_write [PWRAP] write MT6351 Test pass [PWRAP] Read MT6351 Test pass,return_value=0 [PMIC_WRAP]wrap_init pass,the return value=0. DATE_CODE_YY:0, DATE_CODE_WW:0 [SegCode] CS, PROJECT_CODE:0x1A8D, FUNCTION_CODE_0:0x4, FUNCTION_CODE_1:0x0, FAB_CODE:0x0 [LDO] 0:0x9A887879, 1:0x0, 2:0x9B870000, 3:0x9898A [PMIC_PRELOADER] Preloader Start.................. [PMIC_PRELOADER] MT6351 CHIP Code = 0x5120 [PMIC_PRELOADER][pmic_status] Reg[0x2BC]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x21E]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x21A]=0xFFDF [PMIC_PRELOADER][pmic_status] Reg[0x21C]=0x8000 [PMIC_PRELOADER][pmic_status] Reg[0x212]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x214]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x18]=0x8000 [PMIC_PRELOADER][pmic_status] Reg[0x2B6]=0x200 [PMIC_PRELOADER][pmic_status] Reg[0x2A6]=0xC6C [PMIC_PRELOADER][pmic_status] Reg[0x41E]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x420]=0xFF [PMIC_PRELOADER] After Clean register [PMIC_PRELOADER][pmic_status] Reg[0x2BC]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x21E]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x21A]=0xFFDF [PMIC_PRELOADER][pmic_status] Reg[0x21C]=0x8000 [PMIC_PRELOADER][pmic_status] Reg[0x212]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x214]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x18]=0x8000 [PMIC_PRELOADER][pmic_status] Reg[0x2B6]=0x200 [PMIC_PRELOADER][pmic_status] Reg[0x2A6]=0xC6C [PMIC_PRELOADER][pmic_status] Reg[0x41E]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x420]=0xFF [PMIC_PRELOADER][pmic_status] Reg[0x41E]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x420]=0xFF [PMIC_PRELOADER][pmic_status] Reg[0x422]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x12]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0xC]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0xE]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x216]=0xFFFF [PMIC_PRELOADER][pmic_status] Reg[0x218]=0x8000 [PMIC_PRELOADER][pmic_status] Reg[0xA42]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0xA60]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0xA6A]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0xA70]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0xA76]=0x0 [PMIC_PRELOADER][pmic_status] Reg[0x8]=0x0 [PMIC_PRELOADER][pmic_status]After Reg[0x41E]=0x0 [PMIC_PRELOADER]just_rst = 0 bat is exist. [PMIC_PRELOADER] turn off usbdl wo battery.................. [PMIC_PRELOADER][6351] is_efuse_trimed=0x1,[0xC5C]=0x8000 [PMIC_PRELOADER][6351] efuse_data[0x0]=0x16EF [PMIC_PRELOADER][6351] efuse_data[0x1]=0x3 [PMIC_PRELOADER][6351] efuse_data[0x2]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x3]=0xDFA0 [PMIC_PRELOADER][6351] efuse_data[0x4]=0xC054 [PMIC_PRELOADER][6351] efuse_data[0x5]=0x206 [PMIC_PRELOADER][6351] efuse_data[0x6]=0x1400 [PMIC_PRELOADER][6351] efuse_data[0x7]=0x3FC [PMIC_PRELOADER][6351] efuse_data[0x8]=0xFC3C [PMIC_PRELOADER][6351] efuse_data[0x9]=0x57FF [PMIC_PRELOADER][6351] efuse_data[0xA]=0x80 [PMIC_PRELOADER][6351] efuse_data[0xB]=0xF84D [PMIC_PRELOADER][6351] efuse_data[0xC]=0x401F [PMIC_PRELOADER][6351] efuse_data[0xD]=0x4302 [PMIC_PRELOADER][6351] efuse_data[0xE]=0x2223 [PMIC_PRELOADER][6351] efuse_data[0xF]=0x9140 [PMIC_PRELOADER][6351] efuse_data[0x10]=0xA6 [PMIC_PRELOADER][6351] efuse_data[0x11]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x12]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x13]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x14]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x15]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x16]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x17]=0x4 [PMIC_PRELOADER][6351] efuse_data[0x18]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x19]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x1A]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x1B]=0x0 [PMIC_PRELOADER][6351] efuse_data[0x1C]=0x8359 [PMIC_PRELOADER][6351] efuse_data[0x1D]=0x562D [PMIC_PRELOADER][6351] efuse_data[0x1E]=0x541B [PMIC_PRELOADER][6351] efuse_data[0x1F]=0x0 [PMIC_PRELOADER][pmic_init] Reg[0x2B6]=0x201 [fan53526_hw_component_detect] exist = 1, Chip ID = 8108 [fan53526_driver_probe] fan53526_hw_init [0x0]=0xE0 [0x1]=0xE0 [0x2]=0x82 [0x3]=0x81 [0x4]=0x8 [0x5]=0x81 [fan53526_driver_probe] PL g_fan53526_hw_exist=1, g_fan53526_driver_ready=1 [fan53526_driver_probe] PL No I2C_EXT_BUCK_CHANNEL (1) [da9214_hw_component_detect] exist=1, Reg[0x105][7:4]=0xD Enable continuous high speed mode Start Enable continuous high speed mode End [da9214_driver_probe] da9214_hw_init [da9214_driver_probe] PL g_da9214_hw_exist=1, g_da9214_driver_ready=1 [da9214_driver_probe] PL No I2C_EXT_BUCK_CHANNEL (6) [da9214_driver_probe] PL No GPIO_EXT_BUCK_VSEL_PIN (0x0) bat is exist. [PMIC_init] _TOP_CKPDN_CON2:0x367C BIF_BAT_CON0:0x0 LDO_VBIF28:0xDA6A 0x282:0x30E7 0x2b6:0x201 [PMIC_PRELOADER][AUXADC] ch=1 raw=24902 data=4103 [PMIC_init] _TOP_CKPDN_CON2:0x367C BIF_BAT_CON0:0x0 LDO_VBIF28:0xDA6A 0x282:0x30E7 0x2b6:0x201 [PMIC_PRELOADER][AUXADC] ch=2 raw=1178 data=517 [pl_check_bat_protect_status]: check VBAT=4103 mV with 3000 mV, VCHR 4891 mV ,VCHR_HV=6500 start charging... [pl_check_bat_protect_status]: check VBAT=4103 mV with 3000 mV, stop charging... [PMIC_PRELOAault [xxxxEEM] [VCORE] - Kernel Got efuse 0x X [xxxxEEM] [DDR] segment = 1600 [xxxxEEM] [EEM][VCORE] - Preloader Got from DT (0x X, 0x X, 0x X) [HQA]Set NV setting: Vcore = 950 mV(0x38, should be 0x38), Vdram = 1218 mV(0x63, should be 0x63) [PLFM] Init I2C: OK(0) [PLFM] Init PWRAP: OK(0) [PLFM] Init PMIC: OK(0) [PLFM] chip_ver[1] [PTP] >> ptp_init() [PTP] >> get_devinfo() [PTP] << get_devinfo():322 [PTP] >> ptp_init_det() [PTP] PTP read VBOOT from upmu: 0x00003021 [PTP] VCORE voltage bin to 1.5V [PTP] << ptp_init_det():445 [PTP] PTP set volt: 0x00000058 [PTP] M_HW_RES0 = 0x0144926F [PTP] M_HW_RES1 = 0x94E0008D [PTP] M_HW_RES2 = 0x46224000 [PTP] M_HW_RES3 = 0x00000000 [PTP] M_HW_RES4 = 0x00000000 [PTP] M_HW_RES5 = 0x00000000 [PTP] << ptp_init():1040 [BLDR] Build Time: 20181009-030124 [DDR Reserve] ddr reserve mode not be enabled yet ==== Dump RGU Reg ======== RGU MODE: 4D RGU LENGTH: FFE0 RGU STA: 0 RGU INTERVAL: FFF RGU SWSYSRST: 10000 RGU DEBUG_CTL: 200F1 RGU LATCH_CTL: 0 RGU DEBUG1: 0 ==== Dump RGU Reg End ==== RGU: g_rgu_satus:0 mtk_wdt_mode_config mode value=10, tmp:22000010 PL P ON WDT does not trigger reboot mtk_wdt_mode_config mode value=5D, tmp:2200005D RGU mtk_wdt_init:MTK_WDT_DEBUG_CTL(200F3), MTK_WDT_LATCH_CTL(0) WDT IRQ_EN=0x340006 WDT REQ_EN=0x3C0002 Enter mtk_kpd_gpio_set! after set KP enable: KP_SEL = 0x1C70 ! before clk_buf_enable_clkbuf4: 0x1022B100 = 0x4B84A264 clk_buf_enable_clkbuf4: 0x1022B100 = 0x1869557 [RTC] get_frequency_meter: input=0x0, ouput=5 [RTC] get_frequency_meter: input=0x0, ouput=3966 [RTC] get_frequency_meter: input=0x0, ouput=5 [RTC] get_frequency_meter: input=0x0, ouput=0 [RTC] get_frequency_meter: input=0x0, ouput=0 [RTC] rtc_boot_check1 powerkey1 = 0xA357, powerkey2 = 0x67D2 [RTC] bbpu = 0x1, con = 0x4A6, osc32con = 0x7A00, sec = 0x4B3, yea = 0xC032 [RTC] rtc_boot_check2 powerkey1 = 0xA357, powerkey2 = 0x67D2 [RTC] rtc_boot_check Writeif_unlock [RTC] RTC_SPAR0=0x40 [RTC] rtc_2sec_reboot_check 0x4B3 [RTC] irqsta = 0x0, pdn1 = 0x0, pdn2 = 0x201, spar0 = 0x40, spar1 = 0x800 [RTC] new_spare0 = 0x5603, new_spare1 = 0x5, new_spare2 = 0x1, new_spare3 = 0xB [RTC] bbpu = 0x1, con = 0x486, cali = 0x4B3 [PMIC_PRELOADER] pl pmic powerkey Press power key is pressed bat is exist. [PLFM] Power key boot! [RTC] enable_dcxo first bbpu = 0x1, con = 0x486, osc32con = 0x7B00, sec = 0x4B3, yea = 0xC032 [RTC] rtc_bbpu_power_on done [RTC] rtc_enable_2sec_reboot config 0x5F3 EMI_MPUX=1 1st EMI_MPUX=0 2nd [DRAM Klog] init SRAM space for Klog at 2018/11/5 3:14:14 [EMI] mcp_dram_num:0,discrete_dram_num:5,enable_combo_dis:1 emi_settings[0].MODE_REG_5:6,emi_settings[0].type:3, vender_id=6 emi_settings[0].DRAM_RANK_SIZE[0]:0x60000000, DRAM_RANK_SIZE[1]:0x60000000, rank0_size:0x80000000, rankl_size:0x80000000 emi_settings[1].MODE_REG_5:6,emi_settings[1].type:3, vender_id=6 emi_settings[1].DRAM_RANK_SIZE[0]:0x80000000, DRAM_RANK_SIZE[1]:0x80000000, rank0_size:0x80000000, rankl_size:0x80000000 found:1,i:1 [EMI] MDL number = 1 DdrPhySetting_Everest_LP3()+DramcSetting_Everest_LP3() [MEM] 1st complex R/W mem test pass (start addr:0x46000000) 0:dram_rank_size:80000000 1:dram_rank_size:80000000 dram_rank_size[0] = 0x80000000 dram_rank_size[1] = 0x80000000 dram_rank_size[2] = 0x0 dram_rank_size[3] = 0x0 [Enable 4GB Support] Total_dram_size = 0x0000000100000000 ,flag:0x1RGU rgu_dram_reserved:MTK_WDT_MODE(2200005D) [Dram_Buffer] dram_buf_t size: 0x9C280 [Dram_Buffer] part_hdr_t size: 0x200 [Dram_Buffer] sizeof(boot_arg_t): 0xD08 [Dram_Buffer] g_dram_buf start addr: 0x44800000 [Dram_Buffer] g_dram_buf->msdc_gpd_pool start addr: 0x4489C1C0 [Dram_Buffer] g_dram_buf->msdc_bd_pool start addr: 0x4489C200 RAM_CONSOLE using default RAM_CONSOLE start: 0x12D000, size: 0xC00, sig: 0x69AFE4BF RAM_CONSOLE wdt status (0x0)=0x0 [msdc_init]: msdc0 Host controller intialization start [SD0] SET_CLK(260kHz): SCLK(259kHz) MODE(0) DDR(0) DIV(385) DS(0) RS(0) [msdc_init]: msdc0 Host controller intialization done [SD0] Switch to High-Speed mode! [SD0] SET_CLK(260kHz): SCLK(259kHz) MODE(2) DDR(1) DIV(192) DS(0) RS(0) [SD0] Switch to DDR50 mode! [SD0] SET_CLK(52000kHz): SCLK(50000kHz) MODE(2) DDR(1) DIV(1) DS(0) RS(0) [mmc_init_card]: finish successfully [PLFM] Init Boot Device: OK(0) 0:dram_rank_size:80000000 1:dram_rank_size:80000000 0:dram_rank_size:80000000 1:dram_rank_size:80000000 orig_dram_info[0] start: 0x0000000040000000, size: 0x0000000080000000 orig_dram_info[1] start: 0x00000000C0000000, size: 0x0000000080000000 CUSTOM_CONFIG_MAX_DRAM_SIZE: 0x0000000100000000 [Enable 4GB Support] 4GB_flag 0x1 total_dram_size: 0x0000000100000000, max_dram_size: 0x0000000100000000 [GPT_PL]Parsing Primary GPT now... [GPT_PL][0]name=recovery, part_id=8, start_sect=0x40, nr_sects=0x8000 [GPT_PL][1]name=para, part_id=8, start_sect=0x8040, nr_sects=0x400 [GPT_PL][2]name=expdb, part_id=8, start_sect=0x8440, nr_sects=0x5000 [GPT_PL][3]name=frp, part_id=8, start_sect=0xD440, nr_sects=0x800 [GPT_PL][4]name=nvcfg, part_id=8, start_sect=0xDC40, nr_sects=0x4000 [GPT_PL][5]name=nvdata, part_id=8, start_sect=0x11C40, nr_sects=0x10000 [GPT_PL][6]name=metadata, part_id=8, start_sect=0x21C40, nr_sects=0x10000 [GPT_PL][7]name=protect1, part_id=8, start_sect=0x31C40, nr_sects=0x4000 [GPT_PL][8]name=protect2, part_id=8, start_sect=0x35C40, nr_sects=0x63C0 [GPT_PL][9]name=seccfg, part_id=8, start_sect=0x3C000, nr_sects=0x4000 [GPT_PL][10]name=oemkeystore, part_id=8, start_sect=0x40000, nr_sects=0x1000 [GPT_PL][11]name=proinfo, part_id=8, start_sect=0x41000, nr_sects=0x1800 [GPT_PL][12]name=md1img, part_id=8, start_sect=0x42800, nr_sects=0xC000 [GPT_PL][13]name=md1dsp, part_id=8, start_sect=0x4E800, nr_sects=0x2000 [GPT_PL][14]name=md1arm7, part_id=8, start_sect=0x50800, nr_sects=0x1800 [GPT_PL][15]name=md3img, part_id=8, start_sect=0x52000, nr_sects=0x2800 [GPT_PL][16]name=scp1, part_id=8, start_sect=0x54800, nr_sects=0x800 [GPT_PL][17]name=scp2, part_id=8, start_sect=0x55000, nr_sects=0x800 [GPT_PL][18]name=nvram, part_id=8, start_sect=0x55800, nr_sects=0x2800 [GPT_PL][19]name=lk, part_id=8, start_sect=0x58000, nr_sects=0x400 [GPT_PL][20]name=lk2, part_id=8, start_sect=0x58400, nr_sects=0x400 [GPT_PL][21]name=boot, part_id=8, start_sect=0x58800, nr_sects=0x8000 [GPT_PL][22]name=logo, part_id=8, start_sect=0x60800, nr_sects=0x4000 [GPT_PL][23]name=tee1, part_id=8, start_sect=0x64800, nr_sects=0x2800 [GPT_PL][24]name=tee2, part_id=8, start_sect=0x67000, nr_sects=0x2800 [GPT_PL][25]name=keystore, part_id=8, start_sect=0x69800, nr_sects=0x6800 [GPT_PL][26]name=system, part_id=8, start_sect=0x70000, nr_sects=0x500000 [GPT_PL][27]name=cache, part_id=8, start_sect=0x570000, nr_sects=0xD8000 [GPT_PL][28]name=userdata, part_id=8, start_sect=0x648000, nr_sects=0x6E2BFDF [GPT_PL][29]name=flashinfo, part_id=8, start_sect=0x7473FDF, nr_sects=0x8000 [GPT_PL]Success to find valid GPT. PL_LOG_STORE:sram->sig value 0xC726B939! PL_LOG_STORE:sram header is not match, format all! PL_LOG_STORE:set ram_header->sig = 0xABCD1234 PL_LOG_STORE:log_to_emmc function flag 0x0! PL_LOG_STORE:sram_dram_buff->sig 0x0! mblock[0].start: 0x0000000040000000, sz: 0x0000000040000000, limit: 0x00000000C0000000, max_addr: 0x0000000000000000, max_rank: 2, target: -1, mblock[].rank: 0, reserved_addr: 0x000000007FF0 mblock_reserve dbg[0]: 0, 1, 1, 1, 1 mblock[1].start: 0x0000000080000000, sz: 0x0000000080000000, limit: 0x00000000C0000000, max_addr: 0x0000000080000000, max_rank: 2, target: 0, mblock[].rank: 1, reserved_addr: 0x00000000BFFC0 mblock_reserve dbg[1]: 1, 1, 1, 1, 1 mblock[2].start: 0x0000000100000000, sz: 0x0000000040000000, limit: 0x00000000C0000000, max_addr: 0x0000000100000000, max_rank: 2, target: 1, mblock[].rank: 0, reserved_addr: 0x00000000BFFC0 mblock_reserve dbg[2]: 1, 0, 1, 1, 1 mblock[1]: 0000000080000000, 000000003FFC0000 from mblock mblock[2]: 00000000C0000000, 0000000040000000 from mblock mblock_reserve: 00000000BFFC0000 - 00000000C0000000 from mblock 1 mblock-debug[0].start: 0x0000000040000000, sz: 0x0000000040000000 mblock-debug[1].start: 0x0000000080000000, sz: 0x000000003FFC0000 mblock-debug[2].start: 0x00000000C0000000, sz: 0x0000000040000000 mblock-debug[3].start: 0x0000000100000000, sz: 0x0000000040000000 PL_LOG_STORE:sram_header 0x12DC00,sig 0xABCD1234, sram_dram_buff 0x12DC18, buf_addr 0xBFFC0000, pl_buff_header 0xBFFC0000! [PART] blksz: 512B [PART] [0x0000000000008000-0x0000000001007FFF] "recovery" (32768 blocks) [PART] [0x0000000001008000-0x0000000001087FFF] "para" (1024 blocks) [PART] [0x0000000001088000-0x0000000001A87FFF] "expdb" (20480 blocks) [PART] [0x0000000001A88000-0x0000000001B87FFF] "frp" (2048 blocks) [PART] [0x0000000001B88000-0x0000000002387FFF] "nvcfg" (16384 blocks) [PART] [0x0000000002388000-0x0000000004387FFF] "nvdata" (65536 blocks) [PART] [0x0000000004388000-0x0000000006387FFF] "metadata" (65536 blocks) [PART] [0x0000000006388000-0x0000000006B87FFF] "protect1" (16384 blocks) [PART] [0x0000000006B88000-0x00000000077FFFFF] "protect2" (25536 blocks) [PART] [0x0000000007800000-0x0000000007FFFFFF] "seccfg" (16384 blocks) [PART] [0x0000000008000000-0x00000000081FFFFF] "oemkeystore" (4096 blocks) [PART] [0x0000000008200000-0x00000000084FFFFF] "proinfo" (6144 blocks) [PART] [0x0000000008500000-0x0000000009CFFFFF] "md1img" (49152 blocks) [PART] [0x0000000009D00000-0x000000000A0FFFFF] "md1dsp" (8192 blocks) [PART] [0x000000000A100000-0x000000000A3FFFFF] "md1arm7" (6144 blocks) [PART] [0x000000000A400000-0x000000000A8FFFFF] "md3img" (10240 blocks) [PART] [0x000000000A900000-0x000000000A9FFFFF] "scp1" (2048 blocks) [PART] [0x000000000AA00000-0x000000000AAFFFFF] "scp2" (2048 blocks) [PART] [0x000000000AB00000-0x000000000AFFFFFF] "nvram" (10240 blocks) [PART] [0x000000000B000000-0x000000000B07FFFF] "lk" (1024 blocks) [PART] [0x000000000B080000-0x000000000B0FFFFF] "lk2" (1024 blocks) [PART] [0x000000000B100000-0x000000000C0FFFFF] "boot" (32768 blocks) [PART] [0x000000000C100000-0x000000000C8FFFFF] "logo" (16384 blocks) [PART] [0x000000000C900000-0x000000000CDFFFFF] "tee1" (10240 blocks) [PART] [0x000000000CE00000-0x000000000D2FFFFF] "tee2" (10240 blocks) [PART] [0x000000000D300000-0x000000000DFFFFFF] "keystore" (26624 blocks) [PART] [0x000000000E000000-0x00000000ADFFFFFF] "system" (5242880 blocks) [PART] [0x00000000AE000000-0x00000000C8FFFFFF] "cache" (884736 blocks) [PART] [0x00000000C9000000-0x0000000E8E7FBDFF] "userdata" (115523551 blocks) [PART] [0x0000000E8E7FBE00-0x0000000E8F7FBDFF] "flashinfo" (32768 blocks) [ROM_INFO] 'v2','0x0','0x0','0x0','0x2C00' [SEC] AES Legacy : 0 [SEC] SECCFG AC : 1 [LIB] Loading SEC config [LIB] Name = [LIB] Config = 0x22, 0x22 [LIB] SECRO (ac, ac_offset, ac_length) = (0x1, 0x40, 0x40) 0x31,0x41,0x35,0x35 [SEC] DBGPORT 00000051 0000FFFF 00000101 00000101 0022352D 0022D383 00000051 0000FFFF 00000101 0000FFFF 00000101 00000042 00000000 [SEC] DBGPORT (0 1) [SEC] DBGPORT 00000051 0000FFFF 00000101 00000101 0022352D 0022D383 00000051 0000FFFF 00000101 0000FFFF 00000101 00000042 00000000 [SEC] read '0x7800000' 0x4D,0x4D,0x4D,0x4D,0x4,0x0,0x0,0x0, [LIB] seclib_img_auth_load_sig [LIB] CFG read size '0x2000' '0x3C' 0x4D4D4D4D [LIB] SEC CFG 'v4' exists [LIB] HW DEC GCPU Enhance,V1.1 [LIB] SEC CFG is valid. Lock state is 1 �����������[BLDR] Tool connection is unlocked platform_vusb_on VUSB33 is on platform_vusb_on VA10 is on platform_vusb_on VA10 select to 0.95V [PMIC_PRELOADER] pmic_IsUsbCableIn 1 step A1 : Apple 2.1A CHARGER! [TOOL] PMIC not dectect usb cable! [TOOL] <UART> listen ended, receive size:0! [TOOL] <UART> wait sync time 150ms->5ms [TOOL] <UART> receieved data: () Device APC domain init setup: Domain Setup (0x0) Domain Setup (0x0) Domain Setup (0x0) Domain Setup (0x0) Domain Setup (0x0) Device APC domain after setup: Domain Setup (0x0) Domain Setup (0x10003000) Domain Setup (0x5511011) Domain Setup (0x260) Domain Setup (0x6) (B)tz_dapc_sec_init is 0x0 (E)tz_dapc_sec_init is 0x0 (E)MAS0=0x20 (E)MAS1=0x0 mblock[0].start: 0x0000000040000000, sz: 0x0000000040000000, limit: 0x00000000C0000000, max_addr: 0x0000000000000000, max_rank: 3, target: -1, mblock[].rank: 0, reserved_addr: 0x000000007FF0 mblock_reserve dbg[0]: 0, 1, 1, 1, 1 mblock[1].start: 0x0000000080000000, sz: 0x000000003FFC0000, limit: 0x00000000C0000000, max_addr: 0x0000000080000000, max_rank: 3, target: 0, mblock[].rank: 1, reserved_addr: 0x00000000BFF80 mblock_reserve dbg[1]: 0, 1, 1, 1, 1 mblock[2].start: 0x00000000C0000000, sz: 0x0000000040000000, limit: 0x00000000C0000000, max_addr: 0x00000000BFFC0000, max_rank: 3, target: 1, mblock[].rank: 1, reserved_addr: 0x00000000BFFC0 mblock_reserve dbg[2]: 1, 0, 1, 1, 1 mblock[3].start: 0x0000000100000000, sz: 0x0000000040000000, limit: 0x00000000C0000000, max_addr: 0x00000000BFFC0000, max_rank: 3, target: 1, mblock[].rank: 0, reserved_addr: 0x00000000BFFC0 mblock_reserve dbg[3]: 1, 0, 1, 1, 1 mblock_reserve: 00000000BFF80000 - 00000000BFFC0000 from mblock 1 mblock-debug[0].start: 0x0000000040000000, sz: 0x0000000040000000 mblock-debug[1].start: 0x0000000080000000, sz: 0x000000003FF80000 mblock-debug[2].start: 0x00000000C0000000, sz: 0x0000000040000000 mblock-debug[3].start: 0x0000000100000000, sz: 0x0000000040000000 [BLDR] lk active = 4, lk2 active = 0 [BLDR] Loading LK Partition... [PART] partition name = lk [LIB] NS-CHIP [SEC_POLICY] sboot_state = 0x0 [SEC_POLICY] lock_state(default) = 0x4 [PART] img_auth_required = 0 [PART] partition hdr (1) [PART] Image with part header [PART] name : lk [PART] addr : FFFFFFFFh mode : -1 [PART] size : 474500 [PART] magic: 58881688h [PART] part: lk img: lk cert vfy(0 ms) [PART] load "lk" from 0x000000000B000200 (dev) to 0x46000000 (mem) [SUCCESS] [PART] load speed: 10775KB/s, 474500 bytes, 43ms [PART] part: lk img: lk vfy(0 ms) LK addr: 0x46000000, size: 0x74630 [PART] partition name = tee1 [LIB] NS-CHIP [SEC_POLICY] sboot_state = 0x0 [SEC_POLICY] lock_state(default) = 0x4 [PART] img_auth_required = 0 [PART] partition hdr (1) [PART] Image with part header [PART] name : atf [PART] addr : FFFFFFFFh mode : 0 [PART] size : 93696 [PART] magic: 58881688h [PART] part: tee1 img: atf cert vfy(0 ms) [PART] load "tee1" from 0x000000000C900200 (dev) to 0x1005C0 (mem) [SUCCESS] [PART] load speed: 9149KB/s, 93696 bytes, 10ms [PART] part: tee1 img: atf vfy(0 ms) [BLDR] bldr load tee part ret=0x0, addr=0x1005C0 g_da9214_hw_exist=1 [PICACHU] SBP-B-V7 [PICACHU] ac on [PICACHU] SB-L-V7 [PICACHU] ac on bat is exist. [PLFM] boot to LK by ATAG. [xxxx1][preloader]first_volt = 0x68 [xxxx1][preloader]second_volt = 0x58 [xxxx1][preloader]third_volt = 0x48 [xxxx1][preloader]have_550 = 0x0 BOOT_REASON: 0 BOOT_MODE: 0 META_COM TYPE: 0 META_COM ID: 0 META_COM PORT: 285220864 LOG_COM PORT: 285220864 LOG_COM BAUD: 921600 LOG_COM EN: 1 MEM_NUM: 2 MEM_SIZE: 0x80000000 MEM_SIZE: 0x80000000 mblock num: 0x4 mblock start: 0x0000000040000000 mblock size: 0x0000000040000000 mblock rank: 0x0 mblock start: 0x0000000080000000 mblock size: 0x000000003FF80000 mblock rank: 0x1 mblock start: 0x00000000C0000000 mblock size: 0x0000000040000000 mblock rank: 0x1 mblock start: 0x0000000100000000 mblock size: 0x0000000040000000 mblock rank: 0x0 orig_dram num: 0x2 orig_dram start: 0x0000000040000000 orig_dram size: 0x0000000080000000 orig_dram start: 0x00000000C0000000 orig_dram size: 0x0000000080000000 orig_dram start: 0x0000000000000000 orig_dram size: 0x0000000000000000 orig_dram start: 0x0000000000000000 orig_dram size: 0x0000000000000000 lca start: 0x0000000000000000 lca size: 0x0000000000000000 tee start: 0x00000000BFF80000 tee size: 0x0000000000040000 MD_INFO: 0x0 MD_INFO: 0x0 MD_INFO: 0x0 MD_INFO: 0x0 BOOT_TIME: 1488 DA_INFO: 0x0 DA_INFO: 0x0 DA_INFO: 0x0 DA_INFO: 0x0 DA_INFO: 0x0 SEC_INFO: 0x0 SEC_INFO: 0x0 PART_NUM: 2 PART_INFO: 0x44879A84 EFLAG: 1 DDR_RESERVE: 0 DDR_RESERVE: 0 DDR_RESERVE: 38146 DRAM_BUF: 639616 SRAM start: 0x12A000 SRAM size: 0x6000 [TZ_INIT] atf_log_port : 0x11002000 [TZ_INIT] atf_log_baudrate : 0xE1000 [TZ_INIT] atf_irq_num : 325 [TZ_INIT] ATF log buffer start : 0xBFF80000 [TZ_INIT] ATF log buffer size : 0x40000 [TZ_INIT] ATF aee buffer start : 0xBFFBC000 [TZ_INIT] ATF aee buffer size : 0x4000 [BLDR] Others, jump to ATF [BLDR] jump to 0x46000000 [BLDR] <0x46000000>=0xEA000007 [BLDR] <0x46000004>=0xEA009AC7 [TZ_SEC_CFG] SRAMROM Secure Addr 0x2A000 [TZ_SEC_CFG] SRAMROM Secure Control 0x40000000 [TZ_SEC_CFG] SRAMROM Secure Control 0x40000B69 [TZ_SEC_CFG] SRAMROM Secure Control 0x51680B69 [TZ_INIT] ATF entry addr, dram addr: 0x101000, 0x44600000 [TZ_EMI_MPU] MPU [0x44600000-0x4460FFFF] [TZ_INIT] set secure memory protection : 0x44600000, 0x4460FFFF (1) [TZ_INIT] Jump to ATF, then 0x46000000 [ATF](0)[0.000007]CPUxGPT reg(201) [ATF](0)[0.000384]BL33 boot argument location=0x4489c240 [ATF](0)[0.001057]BL33 boot argument size=0xd08 [ATF](0)[0.001614]BL33 start addr=0x46000000 [ATF](0)[0.002135]teearg addr=0x100000 [ATF](0)[0.002587]atf_magic=0x4d415446 [ATF](0)[0.003039]tee_support=0x0 [ATF](0)[0.003432]tee_entry=0x0 [ATF](0)[0.003802]tee_boot_arg_addr=0x100100 [ATF](0)[0.004324]atf_log_port=0x11002000 [ATF](0)[0.004810]atf_log_baudrate=0xe1000 [ATF](0)[0.005308]atf_log_buf_start=0xbff80000 [ATF](0)[0.005853]atf_log_buf_size=0x40000 [ATF](0)[0.006351]atf_aee_debug_buf_start=0xbffbc000 [ATF](0)[0.006967]atf_aee_debug_buf_size=0x4000 [ATF](0)[0.007523]atf_irq_num=325 [ATF](0)[0.007916]BL33_START_ADDRESS=0x46000000 [ATF](0)[0.008473]atf chip_code[279] [ATF](0)[0.008879]atf chip_ver[0] [ATF](0)[0.009269]###@@@ MP0_MISC_CONFIG3:0x000f0000 @@@### [ATF](0)[0.009948]###@@@ MP0_MISC_CONFIG3:0x000fe000 @@@### [ATF](0)[0.010635]mmap atf buffer : 0xbff80000, 0x40000 [ATF](0)[0.011410]mmap atf buffer (force 2MB aligned): 0xbfe00000, 0x200000 [ATF](0)[0.012286]###@@@ CPUSYS1 OFF @@@### [ATF](0)[0.012773]power_off_little_cl cl:1 [ATF](0)[0.013270]INFRA_TOPAXI_PROTECTEN1 (0x10001234):0x00000222 [ATF](0)[0.014040]end NOTICE: BL3-1: v1.0(debug):97d1d3d NOTICE: BL3-1: Built : 03:58:21, Oct 9 2018 [ATF](0)[0.017054]crash flag: 0x0 [ATF](0)[0.017431]sta=0x0 int=0xffc [ATF](0)[0.017839]is_power_on_boot: true [ATF](0)[0.021214]mt_log_setup - atf_buf_addr : 0xbff80100 [ATF](0)[0.021831]mt_log_setup - atf_buf_size : 0x29f00 [ATF](0)[0.022445]mt_log_setup - atf_write_pos : 0xbff80100 [ATF](0)[0.023102]mt_log_setup - atf_read_pos : 0xbff80100 [ATF](0)[0.023748]mt_log_setup - atf_buf_lock : 0x0 [ATF](0)[0.024318]mt_log_setup - mt_log_buf_end : 0xbffa9fff [ATF](0)[0.024986]mt_log_setup - ATF_CRASH_LAST_LOG_SIZE : 0x8000 [ATF](0)[0.025708]mt_log_setup - ATF_EXCEPT_BUF_SIZE_PER_CPU : 0x1000 [ATF](0)[0.026472]mt_log_setup - ATF_EXCEPT_BUF_SIZE : 0xa000 [ATF](0)[0.027150]mt_log_setup - PLATFORM_CORE_COUNT : 0xa [ATF](0)[0.027797]mt_log_setup - atf_except_write_pos_per_cpu[0]: 0x0(Hi), 0xbffb2000(Low) [ATF](0)[0.028787]mt_log_setup - atf_except_write_pos_per_cpu[1]: 0x0(Hi), 0xbffb3000(Low) [ATF](0)[0.029778]mt_log_setup - atf_except_write_pos_per_cpu[2]: 0x0(Hi), 0xbffb4000(Low) [ATF](0)[0.030769]mt_log_setup - atf_except_write_pos_per_cpu[3]: 0x0(Hi), 0xbffb5000(Low) [ATF](0)[0.031760]mt_log_setup - atf_except_write_pos_per_cpu[4]: 0x0(Hi), 0xbffb6000(Low) [ATF](0)[0.032751]mt_log_setup - atf_except_write_pos_per_cpu[5]: 0x0(Hi), 0xbffb7000(Low) [ATF](0)[0.033741]mt_log_setup - atf_except_write_pos_per_cpu[6]: 0x0(Hi), 0xbffb8000(Low) [ATF](0)[0.034732]mt_log_setup - atf_except_write_pos_per_cpu[7]: 0x0(Hi), 0xbffb9000(Low) [ATF](0)[0.035723]mt_log_setup - atf_except_write_pos_per_cpu[8]: 0x0(Hi), 0xbffba000(Low) [ATF](0)[0.036713]mt_log_setup - atf_except_write_pos_per_cpu[9]: 0x0(Hi), 0xbffbb000(Low) [ATF](0)[0.037705]mt_log_setup - atf_crash_flag : 0x41544641 [ATF](0)[0.038372]mt_log_setup - atf_crash_log_addr : 0x0 [ATF](0)[0.039008]mt_log_setup - atf_crash_log_size : 0x0 [ATF](0)[0.039643]BL3-1: v1.0(debug):97d1d3d [ATF](0)[0.040139]BL3-1: Built : 03:58:21, Oct 9 2018 INFO: BL3-1: Initializing runtime services [ATF](0)[0.041319][BL31] Jump to FIQD for initialization! INFO: BL3-1: Preparing for EL3 exit to normal world, LK INFO: BL3-1: Next image address = 0x46000000 INFO: BL3-1: Next image spsr = 0x1d3 [ATF](0)[0.043556][BL31] Final dump! [LK_LOG_STORE:lk log_store_init start. LK_LOG_STORE:dram pl/lk log buff mapping start addr = 0xbffc0000, size = 0x40000 LK_LOG_STORE:sram buff header 0x12dc00,buff address 0xbffc0000, sig 0xcdab3412, buff_size 0x40000, pl log size 0x5dab@0x28, lk log size 0x0@0x28! LK_LOG_STORE: buff ready. 11] [PWRAP] pwrap_init_lk [15] [PWRAP] is_pwrap_init_done 1 [25] platform_init() [26] [msdc_init]: msdc0 Host controller intialization start [26] [info][msdc_set_startbit 489] read data start bit at rising edge [27] [info][msdc_config_clksrc] input clock is 400000kHz [28] [SD0] Bus Width: 1 [28] [info][msdc_config_clksrc] input clock is 400000kHz [29] [info][msdc_set_startbit 489] read data start bit at rising edge [29] [SD0] SET_CLK(260kHz): SCLK(259kHz) MODE(0) DDR(0) DIV(385) DS(0) RS(0) [30] [msdc_init]: msdc0 Host controller intialization done [31] [mmc_init]: msdc0 start mmc_init_card() [31] [mmc_init_card]: start [102] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [103] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [106] [SD0] Switch to High-Speed mode! [108] [SD0] Switch to DDR buswidth [108] [info][msdc_config_clksrc] input clock is 400000kHz [109] [info][msdc_set_startbit 489] read data start bit at rising edge [110] [SD0] SET_CLK(260kHz): SCLK(259kHz) MODE(2) DDR(1) DIV(192) DS(0) RS(0) [111] [SD0] Bus Width: 8 [111] [SD0] Size: 59640 MB, Max.Speed: 52000 kHz, blklen(512), nblks(122142720), ro(0) [112] [mmc_init_mem_card 3543][SD0] Initialized, eMMC50 [112] before host->cur_bus_clk(259740) [117] [SD0] Switch to DDR50 mode! [117] [info][msdc_config_clksrc] input clock is 400000kHz [118] [info][msdc_set_startbit 489] read data start bit at rising edge [119] [SD0] SET_CLK(52000kHz): SCLK(50000kHz) MODE(2) DDR(1) DIV(1) DS(0) RS(0) [120] host->cur_bus_clk(50000000) [120] [mmc_init_card]: finish successfully [120] [mt_part_register_device] [121] [partition init] [121] [GPT_LK]Parsing Primary GPT now... [126] [GPT_LK][0]name=recovery, part_id=8, start_sect=0x40, nr_sects=0x8000 [126] [GPT_LK][1]name=para, part_id=8, start_sect=0x8040, nr_sects=0x400 [127] [GPT_LK][2]name=expdb, part_id=8, start_sect=0x8440, nr_sects=0x5000 [128] [GPT_LK][3]name=frp, part_id=8, start_sect=0xd440, nr_sects=0x800 [129] [GPT_LK][4]name=nvcfg, part_id=8, start_sect=0xdc40, nr_sects=0x4000 [130] [GPT_LK][5]name=nvdata, part_id=8, start_sect=0x11c40, nr_sects=0x10000 [131] [GPT_LK][6]name=metadata, part_id=8, start_sect=0x21c40, nr_sects=0x10000 [131] [GPT_LK][7]name=protect1, part_id=8, start_sect=0x31c40, nr_sects=0x4000 [132] [GPT_LK][8]name=protect2, part_id=8, start_sect=0x35c40, nr_sects=0x63c0 [133] [GPT_LK][9]name=seccfg, part_id=8, start_sect=0x3c000, nr_sects=0x4000 [134] [GPT_LK][10]name=oemkeystore, part_id=8, start_sect=0x40000, nr_sects=0x1000 [135] [GPT_LK][11]name=proinfo, part_id=8, start_sect=0x41000, nr_sects=0x1800 [136] [GPT_LK][12]name=md1img, part_id=8, start_sect=0x42800, nr_sects=0xc000 [137] [GPT_LK][13]name=md1dsp, part_id=8, start_sect=0x4e800, nr_sects=0x2000 [138] [GPT_LK][14]name=md1arm7, part_id=8, start_sect=0x50800, nr_sects=0x1800 [138] [GPT_LK][15]name=md3img, part_id=8, start_sect=0x52000, nr_sects=0x2800 [139] [GPT_LK][16]name=scp1, part_id=8, start_sect=0x54800, nr_sects=0x800 [140] [GPT_LK][17]name=scp2, part_id=8, start_sect=0x55000, nr_sects=0x800 [141] [GPT_LK][18]name=nvram, part_id=8, start_sect=0x55800, nr_sects=0x2800 [142] [GPT_LK][19]name=lk, part_id=8, start_sect=0x58000, nr_sects=0x400 [143] [GPT_LK][20]name=lk2, part_id=8, start_sect=0x58400, nr_sects=0x400 [143] [GPT_LK][21]name=boot, part_id=8, start_sect=0x58800, nr_sects=0x8000 [144] [GPT_LK][22]name=logo, part_id=8, start_sect=0x60800, nr_sects=0x4000 [145] [GPT_LK][23]name=tee1, part_id=8, start_sect=0x64800, nr_sects=0x2800 [146] [GPT_LK][24]name=tee2, part_id=8, start_sect=0x67000, nr_sects=0x2800 [147] [GPT_LK][25]name=keystore, part_id=8, start_sect=0x69800, nr_sects=0x6800 [148] [GPT_LK][26]name=system, part_id=8, start_sect=0x70000, nr_sects=0x500000 [149] [GPT_LK][27]name=cache, part_id=8, start_sect=0x570000, nr_sects=0xd8000 [149] [GPT_LK][28]name=userdata, part_id=8, start_sect=0x648000, nr_sects=0x6e2bfdf [150] [GPT_LK][29]name=flashinfo, part_id=8, start_sect=0x7473fdf, nr_sects=0x8000 [151] [GPT_LK]Success to find valid GPT. [152] [SD0] boot device found [152] [PART_LK][get_part] para [157] [LK_BOOT] Load 'para' partition to 0x4611563C (6144 bytes in 5 ms) [158] [PART_LK][get_part] boot [162] [LK_BOOT] Load 'boot' partition to 0x46095630 (2656 bytes in 4 ms) [172] Kernel(1) zimage_size:0x7a955e,dtb_addr:0x460f54d5(dtb_size:0x1feb9) [173] [LK] fdt setup addr:0x44000000 status:1!!! [173] [LEDS]LK: leds_init: mt65xx_backlight_off [174] [LEDS]LK: mt65xx_backlight_off [177] [LEDS]LK:Cannot find LED node from dts [181] [LEDS]LK:Cannot find LED node from dts [184] [LEDS]LK:Cannot find LED node from dts [188] [LEDS]LK:Cannot find LED node from dts [191] [LEDS]LK:Cannot find LED node from dts [195] [LEDS]LK:Cannot find LED node from dts [198] [LEDS]LK:Cannot find LED node from dts [199] Cannot not get the LED info from device tree. [199] [LEDS]LK: lcd-backlight level is 0 [200] [LK_DDP/INFO]error:enable module clock unknow module 16 [400] [PART_LK][get_part] para [405] [LK_ENV]ENV of area 0 initialize sucess [406] [PART_LK][get_part] para [409] [LK_ENV]ENV SIG of area 1 is wrong [409] [LK_ENV]env area: 0 [409] [LK_ENV]env: [409] [LK_ENV]off-mode-charge=1 [410] [LK_ENV]env area: 1 [410] [LK_ENV]no valid env [410] [LK_ENV]get_env usb2jtag from area 0 [411] [USB2JTAG] current setting is 0. [411] [LK_DDP/ddp_manager]scenario display_interface acquire mutex 0 , left mutex 0x1e! [412] [LK_DDP/ddp_manager]assign default irqs table index 0 [413] [LK_DDP/ddp_manager]create handle 0x46075d28 on scenario display_interface [414] [LK_DDP/ddp_manager]set dst module on scenario display_interface, module dsi0 [415] [LK_DDP/ddp_path]ddp_set_dst_module, scenario=display_interface, dst_module=dsi0 [416] [LK_DDP/ddp_path]find module: can not find module dsi0 on scenario display_interface [417] [LK_DDP/ddp_path]ddp_get_dst_module, scneario=display_interface, dst_module=dpi [418] [LK_DDP/ddp_path]scenario display_interface have modules: ovl1 rdma1 dsi0 [419] [LK_DDP/ddp_manager]path set lcm drv handle 0x46075d28 [419] [LK_DDP/ddp_manager]dsi0 set lcm utils [420] [LK_DDP/ddp_manager]path init on scenario display_interface [421] [LK_DDP/ddp_path]ddp path m4u off [421] [LK_DDP/ddp_path]ddp path top clock on [422] [LK_DDP/ddp_path]ddp CG:0 [422] [LK_DDP/ddp_path]mutex sof: dsi0 dst module dsi0 :vido_mode [423] [LK_DDP/ddp_path]mutex 0 value=0x4800, sof=dsi0 [423] [LK_DDP/ddp_path]path connect on scenario display_interface [424] [LK_DDP/ddp_path]connect_path: ovl1 to dsi0 [425] [LK_DDP/ddp_manager]path config ovl 0, rdma 0, wdma 0, dst 1 on handle 0x46075d28 scenario display_interface NT36672 id = 0x80, id1=0x70 [450] [LK_DDP/ddp_manager]path deinit on scenario display_interface [450] [LK_DDP/ddp_path]mutex 0 clear [451] [LK_DDP/ddp_path]path disconnect on scenario display_interface [451] [LK_DDP/ddp_path]disconnect_path: ovl1 to dsi0 [452] [LK_DDP/ddp_path]disconnect mout ovl1 to rdma1 [453] [LK_DDP/ddp_manager]scenario display_interface deinit module ovl1 [454] [LK_DDP/OVL]OVL1DeInit close CG [454] [LK_DDP/INFO]disable ovl1 clk, CG0 0x10000, CG1 0xffffff00,dummy CON = 0xffeffff8 [455] [LK_DDP/ddp_manager]scenario display_interface deinit module rdma1 [456] [LK_DDP/RDMA]RDMA1Deinit [456] [LK_DDP/INFO]disable rdma1 clk, CG0 0x110000, CG1 0xffffff00,dummy CON = 0xfffffff8 [457] [LK_DDP/ddp_manager]scenario display_interface deinit module dsi0 [458] [LK_DDP/INFO]disable dsi0 clk, CG0 0x110000, CG1 0xffffff03,dummy CON = 0xfffffff8 [461] [LK_DDP/ddp_manager]destroy path handle 0x46075d28 on scenario display_interface [462] [LK_DDP/ddp_manager]release mutex 0 , left mutex 0x1f! [463] [LK_DDP/ddp_path]path disconnect on scenario display_interface [463] [LK_DDP/ddp_path]disconnect_path: ovl1 to dsi0 [464] [LK_DDP/ddp_path]disconnect mout ovl1 to rdma1 [465] we will use lcm: aeon_nt36672_fhd_dsi_vdo_x600_xinli [465] mblock_reserve: bdff0000 - bff80000 from mblock 1 [466] FB base = 0xbdff0000, FB size = 0x1f90000 (33095680) [467] fb_va: 0xbdff0000, fb_pa: 0xbdff0000, fb_pa_k: 0xbdff0000 [467] [LK_DDP/ddp_manager]ddp manager init [468] [LK_DDP/ddp_manager]scenario primary_disp acquire mutex 0 , left mutex 0x1e! [469] [LK_DDP/ddp_manager]assign default irqs table index 0 [469] [LK_DDP/ddp_manager]create handle 0x46075d28 on scenario primary_disp [470] [LK_DDP/ddp_manager]set dst module on scenario primary_disp, module dsi0 [471] [LK_DDP/ddp_path]ddp_set_dst_module, scenario=primary_disp, dst_module=dsi0 [472] [LK_DDP/ddp_path]dsi0 is already on path [473] [LK_DDP/ddp_manager]path set lcm drv handle 0x46075d28 [473] [LK_DDP/ddp_manager]dsi0 set lcm utils [474] [LK_DDP/ddp_manager]set scenario primary_disp mode Video Mode [474] [LK_DDP/ddp_manager]path init on scenario primary_disp [475] [LK_DDP/ddp_path]ddp path m4u off [476] [LK_DDP/ddp_path]ddp path top clock on [476] [LK_DDP/ddp_path]ddp CG:110000 [477] [LK_DDP/ddp_path]mutex sof: dsi0 dst module dsi0 :vido_mode [477] [LK_DDP/ddp_path]mutex 0 value=0x5fcb400, sof=dsi0 [478] [LK_DDP/ddp_path]path connect on scenario primary_disp [479] [LK_DDP/ddp_path]connect_path: ovl0 to dsi0 [479] [LK_DDP/ddp_manager]path config ovl 0, rdma 0, wdma 0, dst 1 on handle 0x46075d28 scenario primary_disp [552] [LK/LCM]NT36672--------cmd=0--i2c write success---- [573] [LK/LCM]NT36672--------cmd=1--i2c write success---- [746] [LK_DDP/ddp_manager]map event 7 to irq 0x50004 on scenario primary_disp [747] [LK_DDP/ddp_manager]enable event on scenario primary_disp, event 7, irtbit 0x50004 [748] [LK_DDP/ddp_manager]enable event on scenario primary_disp, event 1, irtbit 0x50004 [758] [LK_DDP/ddp_manager]path check busy on scenario primary_disp [759] [LK_DDP/ddp_manager]path config ovl 1, rdma 0, wdma 0, dst 0 on handle 0x46075d28 scenario primary_disp [760] [LK_DDP/OVL]module 0, layer=3, en=1, src=0, fmt=16785410, addr=0xbe8f8000, x=0, y=0, pitch=4320, dst(0, 0, 1080, 2160),keyEn=0, key=0, aen=1, alpha=255 [762] [LK_DDP/OVL]ovl0, layer=3, source=memory, off(x=0, y=0), dst(0, 0, 1080, 2160),pitch=4320,fmt=eBGRA8888, addr=be8f8000, keyEn=0, key=0, aen=1, alpha=255 [764] [LK_DDP/ddp_manager]path check busy on scenario primary_disp [764] [LK_DDP/ddp_manager]path config ovl 1, rdma 0, wdma 0, dst 0 on handle 0x46075d28 scenario primary_disp [766] [LK_DDP/OVL]module 0, layer=0, en=1, src=0, fmt=16785410, addr=0xbdff0000, x=0, y=0, pitch=4352, dst(0, 0, 1080, 2160),keyEn=0, key=0, aen=1, alpha=255 [767] [LK_DDP/OVL]ovl0, layer=0, source=memory, off(x=0, y=0), dst(0, 0, 1080, 2160),pitch=4352,fmt=eBGRA8888, addr=bdff0000, keyEn=0, key=0, aen=1, alpha=255 [769] [LK_DDP/OVL]module 0, layer=3, en=1, src=0, fmt=16785410, addr=0xbe8f8000, x=0, y=0, pitch=4320, dst(0, 0, 1080, 2160),keyEn=0, key=0, aen=1, alpha=255 [771] [LK_DDP/OVL]ovl0, layer=3, source=memory, off(x=0, y=0), dst(0, 0, 1080, 2160),pitch=4320,fmt=eBGRA8888, addr=be8f8000, keyEn=0, key=0, aen=1, alpha=255 [772] mt_get_logo_db_addr: 0x4e900000 [773] [show_logo_common: fill_rect_with_color_by_32bit 341] [883] fb dump: 0x00000000, 0x00000000, 0x00000000, 0x00000000 [886] [LK_DDP/ddp_manager]path check busy on scenario primary_disp [887] [LK_DDP/ddp_manager]path start on scenario primary_disp [888] [LK_DDP/ddp_manager]dpmgr_path_trigger on scenario primary_disp [888] [LK_DDP/ddp_path]mutex 0 enable [889] s_mt65xx_gd.gdfIndex=3kedump mini start [889] LK Dump: atf_log_init not supported kedump: lkdump debug init ok kedump: boot_reason(0) RAM_CONSOLE. start: 0x12d000, size: 0xc00 RAM_CONSOLE. lk size mismatch 0 + c0 != 100 RAM_CONSOLE. wdt_status 0x0, fiq_step 0x0, exp_type 0x0 [892] detecting pmic just reset [892] [PART_LK][get_part] para [897] [LK_BOOT] Load 'para' partition to 0x4609F654 (6144 bytes in 4 ms) [898] mtk detect key function key = 17 [899] mtk detect key function key = 17 [899] mtk detect key function key = 17 [899] mtk detect key function key = 17 [900] mtk detect key function key = 17 [900] mtk detect key function key = 17 [901] mtk detect key function key = 17 [901] mtk detect key function key = 17 [902] mtk detect key function key = 17 [902] mtk detect key function key = 17 [902] mtk detect key function key = 17 [903] mtk detect key function key = 17 [903] mtk detect key function key = 17 [904] mtk detect key function key = 17 [904] mtk detect key function key = 17 [905] mtk detect key function key = 17 [905] mtk detect key function key = 17 [906] mtk detect key function key = 17 [906] mtk detect key function key = 17 [906] mtk detect key function key = 17 [907] mtk detect key function key = 17 [907] mtk detect key function key = 17 [908] mtk detect key function key = 17 [908] mtk detect key function key = 17 [909] mtk detect key function key = 17 [909] mtk detect key function key = 17 [910] mtk detect key function key = 17 [910] mtk detect key function key = 17 [910] mtk detect key function key = 17 [911] mtk detect key function key = 17 [911] mtk detect key function key = 17 [912] mtk detect key function key = 17 [912] mtk detect key function key = 17 [913] mtk detect key function key = 17 [913] mtk detect key function key = 17 [914] mtk detect key function key = 17 [914] mtk detect key function key = 17 [914] mtk detect key function key = 17 [915] mtk detect key function key = 17 [915] mtk detect key function key = 17 [916] mtk detect key function key = 17 [916] mtk detect key function key = 17 [917] mtk detect key function key = 17 [917] mtk detect key function key = 17 [918] mtk detect key function key = 17 [918] mtk detect key function key = 17 [918] mtk detect key function key = 17 [919] mtk detect key function key = 17 [919] mtk detect key function key = 17 [920] mtk detect key function key = 17 [920] mtk detect key function key = 17 [921] mtk detect key function key = 17 [921] mtk detect key function key = 17 [921] mtk detect key function key = 17 [922] mtk detect key function key = 17 [922] mtk detect key function key = 17 [923] mtk detect key function key = 17 [923] mtk detect key function key = 17 [924] mtk detect key function key = 17 [924] mtk detect key function key = 17 [925] mtk detect key function key = 17 [925] mtk detect key function key = 17 [925] mtk detect key function key = 17 [926] mtk detect key function key = 17 [926] mtk detect key function key = 17 [927] mtk detect key function key = 17 [927] mtk detect key function key = 17 [928] mtk detect key function key = 17 [928] mtk detect key function key = 17 [929] mtk detect key function key = 17 [929] mtk detect key function key = 17 [929] mtk detect key function key = 17 [930] mtk detect key function key = 17 [930] mtk detect key function key = 17 [931] mtk detect key function key = 17 [931] mtk detect key function key = 17 [932] mtk detect key function key = 17 [932] mtk detect key function key = 17 [933] mtk detect key function key = 17 [933] mtk detect key function key = 17 [933] mtk detect key function key = 17 [934] mtk detect key function key = 17 [934] mtk detect key function key = 17 [935] mtk detect key function key = 17 [935] mtk detect key function key = 17 [936] mtk detect key function key = 17 [936] mtk detect key function key = 17 [936] mtk detect key function key = 17 [937] mtk detect key function key = 17 [937] mtk detect key function key = 17 [938] mtk detect key function key = 17 [938] mtk detect key function key = 17 [939] mtk detect key function key = 17 [939] mtk detect key function key = 17 [940] mtk detect key function key = 17 [940] mtk detect key function key = 17 [940] mtk detect key function key = 17 [941] mtk detect key function key = 17 [941] mtk detect key function key = 17 [942] mtk detect key function key = 17 [942] mtk detect key function key = 17 [943] mtk detect key function key = 17 [943] mtk detect key function key = 17 [944] mtk detect key function key = 17 [944] mtk detect key function key = 17 [944] mtk detect key function key = 17 [945] mtk detect key function key = 17 [945] mtk detect key function key = 17 [946] mtk detect key function key = 17 [946] mtk detect key function key = 17 [947] mtk detect key function key = 17 [947] mtk detect key function key = 17 [948] < Kernel Enter Normal Boot > [948] mt_get_logo_db_addr_pa: 0x4e900000 [948] [PART_LK][get_part] logo [949] [PART_LK][get_part] logo [953] ========================================= [953] [LK_BOOT] logo magic number : 0x58881688 [954] [LK_BOOT] logo name : logo [954] [LK_BOOT] logo size : 5178966 [955] ========================================= [SBC] sec_fun_init [1025] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [1026] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [1032] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [1033] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [1036] [SBC] Enter logo check [SBC] NS-CHIP [1037] [SEC_POLICY] sboot_state = 0x0 [1037] [SEC_POLICY] lock_state(default) = 0x4 [1038] [SBC] Consume (2) ms [1038] === mt_dcm_init === [1038] [dcm_set_default]type:0x00001f8e [1039] ******** dcm dump register ********* [1039] mcusys DCM: [1039] MCUCFG_L2C_SRAM_CTRL(0x10220648): 0x200081 [1040] MCUCFG_CCI_CLK_CTRL(0x10220660): 0x117 [1040] MCUCFG_BUS_FABRIC_DCM_CTRL(0x10220668): 0x3F0FFF [1041] MCUCFG_CCI_ADB400_DCM_CONFIG(0x10220740): 0x1E0000FF [1042] MCUCFG_SYNC_DCM_CONFIG(0x10220744): 0x70707 [1042] MCUCFG_SYNC_DCM_CLUSTER_CONFIG(0x1022074C): 0x9090 [1043] === infra DCM === [1043] INFRA_BUS_DCM_CTRL(0x10001070): 0x40780603 [1044] P2P_RX_CLK_ON(0x100010A0): 0xF [1044] INFRA_MISC_2(0x10001F18): 0x10063 [1045] === peri DCM === [1045] PERI_BUS_DCM_CTRL(0x10001074): 0xB0380603 [1045] === MEM DCM === [1046] MEM_DCM_CTRL(0x10001078): 0x3E021BE [1046] DFS_MEM_DCM_CTRL(0x1000107C): 0x318 [1047] [1047] [ccci-off]0.power on MD_INFRA/MODEM_TOP ret=0 [1047] [ccci-off]8.power off ARM7, HSPAL2, LTEL2 [1049] [AUXADC] ch=1 raw=24826 data=4091 [1063] [BATTERY:bq25890] charger enable/disable 1 ! [1064] [bq25890] [1066] [0x0]=0x7f [1066] [0x1]=0x6 [1067] [0x2]=0x91 [1068] [0x3]=0x1a [1068] [0x4]=0x20 [1069] [0x5]=0x12 [1070] [0x6]=0x82 [1070] [0x7]=0x9d [1071] [0x8]=0x9f [1072] [0x9]=0x44 [1073] [0xa]=0x73 [1073] [0xb]=0x2 [1074] [0xc]=0x0 [1075] [0xd]=0x93 [1075] [0xe]=0x5b [1076] [0xf]=0x5b [1077] [0x10]=0x3e [1078] [0x11]=0x15 [1078] [0x12]=0x0 [1079] [0x13]=0x3f [1080] [0x14]=0x6 [1080] [1080] pchr_turn_on_charging: enable charging failed, ret = -95 [1081] pchr_turn_on_charging: dump register failed, ret = -95 [1082] [I2C-LK] 323: id=0,addr: 53, transfer error [1082] [I2C-LK] 329: I2C_ACKERR [1083] [I2C-LK] 205: I2C structure: [I2C-LK] Clk=15600,Id=0,Mode=1,St_rs=0,Dma_en=0,Op=3,Poll_en=1,Irq_stat=2 [I2C-LK] Trans_len=1,Trans_num=2,Trans_auxlen=1,Data_size=ffff,speed=100 [1085] [I2C-LK] 208: base address 0x11007000 [1085] [I2C-LK] 228: I2C register: [I2C-LK] SLAVE_ADDR=a6,INTR_MASK=f8,INTR_STAT=3,CONTROL=38,TRANSFER_LEN=1 [I2C-LK] TRANSAC_LEN=2,DELAY_LEN=2,TIMING=1126,START=0,FIFO_STAT=1101 [I2C-LK] IO_CONFIG=3,HS=102,DCM_EN=0,DEBUGSTAT=40,EXT_CONF=8001,TRANSFER_LEN_AUX=1 [1088] [I2C-LK] 819: write_read 0x10001 bytes fails,ret=-121. [1089] rt9466_i2c_read_byte: I2CR[0x40] failed, code = -1 [1089] mt65xx_bat_init: get primary charger failed [1091] [AUXADC] ch=2 raw=1176 data=516 [1093] [AUXADC] ch=2 raw=1175 data=516 [1093] [Chip_Trim] Reg[0xCB8]=0x0, chip_diff_trim_value_4_0=0 [1094] [Chip_Trim] chip_diff_trim_value=1000 [1094] ******** [fgauge_initialization] reset HW FG! [1095] [fgauge_initialization] Reg[0xcba]=0x0 [1095] [fg_get_data_ready_status] Reg[0xca4]=0x229 [1096] [fg_get_data_ready_status] Reg[0xca4]=0x629 [1096] [fgauge_read_current] : FG_CURRENT = 0 [1097] [fg_get_data_ready_status] Reg[0xca4]=0xc29 [1098] [fg_get_data_ready_status] Reg[0xca4]=0x829 [1098] [fgauge_read_current] current(discharging) = 0 mA [1099] [fgauge_read_current] Auto adjust value due to the Rfg is 10 Ori current=0, [1100] [fgauge_read_current] new current=0 [1100] [fgauge_read_current] ori current=0 [1101] [use_chip_trim_value] 0 -> 0 [1101] [fgauge_read_current] final current=0 (ratio=86) [1102] [fg_get_data_ready_status] Reg[0xca4]=0x229 [1102] [fg_get_data_ready_status] Reg[0xca4]=0x629 [1103] [fgauge_read_current] : FG_CURRENT = 0 [1103] [fg_get_data_ready_status] Reg[0xca4]=0xc29 [1104] [fg_get_data_ready_status] Reg[0xca4]=0x829 [1105] [fgauge_read_current] current(discharging) = 0 mA [1105] [fgauge_read_current] Auto adjust value due to the Rfg is 10 Ori current=0, [1106] [fgauge_read_current] new current=0 [1107] [fgauge_read_current] ori current=0 [1107] [use_chip_trim_value] 0 -> 0 [1107] [fgauge_read_current] final current=0 (ratio=86) [1108] [fg_get_data_ready_status] Reg[0xca4]=0x229 [1109] [fg_get_data_ready_status] Reg[0xca4]=0x629 [1109] [fgauge_read_current] : FG_CURRENT = 0 [1110] [fg_get_data_ready_status] Reg[0xca4]=0xc29 [1110] [fg_get_data_ready_status] Reg[0xca4]=0x829 [1111] [fgauge_read_current] current(discharging) = 0 mA [1112] [fgauge_read_current] Auto adjust value due to the Rfg is 10 Ori current=0, [1113] [fgauge_read_current] new current=0 [1113] [fgauge_read_current] ori current=0 [1114] [use_chip_trim_value] 0 -> 0 [1114] [fgauge_read_current] final current=0 (ratio=86) [1115] [fg_get_data_ready_status] Reg[0xca4]=0x229 [1115] [fg_get_data_ready_status] Reg[0xca4]=0x629 [1116] [fgauge_read_current] : FG_CURRENT = 0 [1116] [fg_get_data_ready_status] Reg[0xca4]=0xc29 [1117] [fg_get_data_ready_status] Reg[0xca4]=0x829 [1117] [fgauge_read_current] current(discharging) = 0 mA [1118] [fgauge_read_current] Auto adjust value due to the Rfg is 10 Ori current=0, [1119] [fgauge_read_current] new current=0 [1119] [fgauge_read_current] ori current=0 [1120] [use_chip_trim_value] 0 -> 0 [1120] [fgauge_read_current] final current=0 (ratio=86) [1121] [fg_get_data_ready_status] Reg[0xca4]=0x229 [1122] [fg_get_data_ready_status] Reg[0xca4]=0x629 [1122] [fgauge_read_current] : FG_CURRENT = fd89 [1123] [fg_get_data_ready_status] Reg[0xca4]=0xc29 [1123] [fg_get_data_ready_status] Reg[0xca4]=0x829 [1124] [fgauge_read_current] current(discharging) = 996 mA [1125] [fgauge_read_current] Auto adjust value due to the Rfg is 10 Ori current=996, [1125] [fgauge_read_current] new current=1992 [1126] [fgauge_read_current] ori current=1992 [1127] [use_chip_trim_value] 1713 -> 1713 [1127] [fgauge_read_current] final current=1713 (ratio=86) [1128] ******** [fgauge_initialization] Done! [1142] [BATTERY:bq25890] charger enable/disable 0 ! [1142] [bq25890] [1144] [0x0]=0x7f [1145] [0x1]=0x6 [1146] [0x2]=0x91 [1146] [0x3]=0xa [1147] [0x4]=0x20 [1148] [0x5]=0x12 [1148] [0x6]=0x82 [1149] [0x7]=0x9d [1150] [0x8]=0x9f [1151] [0x9]=0x44 [1151] [0xa]=0x73 [1152] [0xb]=0x2 [1153] [0xc]=0x0 [1153] [0xd]=0x93 [1154] [0xe]=0x5a [1155] [0xf]=0x5a [1155] [0x10]=0x3e [1156] [0x11]=0x0 [1157] [0x12]=0x0 [1158] [0x13]=0x3f [1158] [0x14]=0x6 [1159] [1159] pchr_turn_on_charging: disable charging failed, ret = -95 [1159] pchr_turn_on_charging: dump register failed, ret = -95 [1231] [fgauge_read_IM_current] : FG_CURRENT = fd83 [1232] [fgauge_read_IM_current] current(discharging) = 1005 mA [1232] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1005, [1233] [fgauge_read_IM_current] new current=2010 [1234] [fgauge_read_IM_current] ori current=2010 [1234] [use_chip_trim_value] 1728 -> 1728 [1235] [fgauge_read_IM_current] final current=1728 (ratio=86) [1256] [fgauge_read_IM_current] : FG_CURRENT = fc5e [1257] [fgauge_read_IM_current] current(discharging) = 1468 mA [1257] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1468, [1258] [fgauge_read_IM_current] new current=2936 [1259] [fgauge_read_IM_current] ori current=2936 [1260] [use_chip_trim_value] 2524 -> 2524 [1260] [fgauge_read_IM_current] final current=2524 (ratio=86) [1261] [6,Calculate Rac] 41002,40822,1728,2524,226,226,0 [1281] [fgauge_read_IM_current] : FG_CURRENT = fd80 [1281] [fgauge_read_IM_current] current(discharging) = 1010 mA [1282] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1010, [1283] [fgauge_read_IM_current] new current=2020 [1283] [fgauge_read_IM_current] ori current=2020 [1284] [use_chip_trim_value] 1737 -> 1737 [1284] [fgauge_read_IM_current] final current=1737 (ratio=86) [1306] [fgauge_read_IM_current] : FG_CURRENT = fc5b [1306] [fgauge_read_IM_current] current(discharging) = 1473 mA [1307] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1473, [1308] [fgauge_read_IM_current] new current=2946 [1308] [fgauge_read_IM_current] ori current=2946 [1309] [use_chip_trim_value] 2533 -> 2533 [1309] [fgauge_read_IM_current] final current=2533 (ratio=86) [1310] [6,Calculate Rac] 40986,40809,1737,2533,222,222,0 [1330] [fgauge_read_IM_current] : FG_CURRENT = fd7d [1331] [fgauge_read_IM_current] current(discharging) = 1015 mA [1331] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1015, [1332] [fgauge_read_IM_current] new current=2030 [1333] [fgauge_read_IM_current] ori current=2030 [1333] [use_chip_trim_value] 1745 -> 1745 [1334] [fgauge_read_IM_current] final current=1745 (ratio=86) [1355] [fgauge_read_IM_current] : FG_CURRENT = fd7b [1356] [fgauge_read_IM_current] current(discharging) = 1018 mA [1356] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1018, [1357] [fgauge_read_IM_current] new current=2036 [1358] [fgauge_read_IM_current] ori current=2036 [1358] [use_chip_trim_value] 1750 -> 1750 [1359] [fgauge_read_IM_current] final current=1750 (ratio=86) [1360] [4,Calculate Rac] bypass due to (curr_x-curr_y) < 40mA [1360] [6,Calculate Rac] 40974,40658,1745,1750,0,-1,0 [1380] [fgauge_read_IM_current] : FG_CURRENT = fd7c [1381] [fgauge_read_IM_current] current(discharging) = 1016 mA [1381] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1016, [1382] [fgauge_read_IM_current] new current=2032 [1383] [fgauge_read_IM_current] ori current=2032 [1383] [use_chip_trim_value] 1747 -> 1747 [1384] [fgauge_read_IM_current] final current=1747 (ratio=86) [1405] [fgauge_read_IM_current] : FG_CURRENT = fc5c [1406] [fgauge_read_IM_current] current(discharging) = 1472 mA [1406] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1472, [1407] [fgauge_read_IM_current] new current=2944 [1408] [fgauge_read_IM_current] ori current=2944 [1408] [use_chip_trim_value] 2531 -> 2531 [1409] [fgauge_read_IM_current] final current=2531 (ratio=86) [1410] [6,Calculate Rac] 40976,40818,1747,2531,201,201,1 [1430] [fgauge_read_IM_current] : FG_CURRENT = fd82 [1430] [fgauge_read_IM_current] current(discharging) = 1007 mA [1431] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1007, [1432] [fgauge_read_IM_current] new current=2014 [1432] [fgauge_read_IM_current] ori current=2014 [1433] [use_chip_trim_value] 1732 -> 1732 [1433] [fgauge_read_IM_current] final current=1732 (ratio=86) [1455] [fgauge_read_IM_current] : FG_CURRENT = fc5a [1455] [fgauge_read_IM_current] current(discharging) = 1475 mA [1456] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1475, [1457] [fgauge_read_IM_current] new current=2950 [1457] [fgauge_read_IM_current] ori current=2950 [1458] [use_chip_trim_value] 2537 -> 2537 [1458] [fgauge_read_IM_current] final current=2537 (ratio=86) [1459] [6,Calculate Rac] 40971,40806,1732,2537,204,204,0 [1479] [fgauge_read_IM_current] : FG_CURRENT = fd7a [1480] [fgauge_read_IM_current] current(discharging) = 1019 mA [1480] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1019, [1481] [fgauge_read_IM_current] new current=2038 [1482] [fgauge_read_IM_current] ori current=2038 [1482] [use_chip_trim_value] 1752 -> 1752 [1483] [fgauge_read_IM_current] final current=1752 (ratio=86) [1504] [fgauge_read_IM_current] : FG_CURRENT = fc5e [1505] [fgauge_read_IM_current] current(discharging) = 1468 mA [1505] [fgauge_read_IM_current] Auto adjust value due to the Rfg is 10 Ori current=1468, [1506] [fgauge_read_IM_current] new current=2936 [1507] [fgauge_read_IM_current] ori current=2936 [1507] [use_chip_trim_value] 2524 -> 2524 [1508] [fgauge_read_IM_current] final current=2524 (ratio=86) [1509] [6,Calculate Rac] 40976,40808,1752,2524,217,217,0 [1509] [dlpt_R] 226,222,201,204,217 [201:226:5]214 [1563] [AUXADC] ch=1 raw=24898 data=4103 [1563] [check_bat_protect_status]: check VBAT=4103 mV with 3450 mV, stop charging... [1564] mt_get_logo_db_addr: 0x4e900000 [1564] mt_get_tempfb_addr: 0xbf200000 ,fb_addr 0xbdff0000 [1565] [show_animation_common: check_logo_index_valid 71]logonum =57, index =0 [1566] show_animation_common, in_addr=0x4e9000ec, logolen=945366 [1567] [decompress_logo decompress_logo 48]in=0x4e9000ec, out=0xbf200000, inlen=945366, logolen=9469952 [1659] [decompress_logo decompress_logo 97]have=9331200 [1660] [show_animation_common: fill_animation_logo 124]bits = 32 [1660] [show_logo_common: fill_rect_with_content 427] [1661] [show_logo_common: fill_rect_with_content_by_32bit_argb8888 128] [1662] [show_logo_common]dst_addr= 0xff060208, color_addr= 0xff060208, i= 0, j=0 [1663] [show_logo_common]dst_addr= 0xff030305, color_addr= 0xff030305, i= 0, j=2159 [1859] [show_logo_common]dst_addr= 0xff070209, color_addr= 0xff070209, i= 1079, j=0 [1860] [show_logo_common]dst_addr= 0xff030305, color_addr= 0xff030305, i= 1079, j=2159 [1861] fb dump: 0xff030305, 0xff030305, 0xff030305, 0xff030305 [1865] [LK_DDP/ddp_manager]path check busy on scenario primary_disp [1865] [LK_DDP/ddp_manager]dsi0 is busy [1866] [LEDS]LK: mt65xx_backlight_on:level = 255 [1869] [LEDS]LK:Cannot find LED node from dts [1873] [LEDS]LK:Cannot find LED node from dts [1876] [LEDS]LK:Cannot find LED node from dts [1880] [LEDS]LK:Cannot find LED node from dts [1883] [LEDS]LK:Cannot find LED node from dts [1887] [LEDS]LK:Cannot find LED node from dts [1890] [LEDS]LK:Cannot find LED node from dts [1890] Cannot not get the LED info from device tree. [1891] [LEDS]LK: lcd-backlight level is 255 [1892] fb dump: 0xff030305, 0xff030305, 0xff030305, 0xff030305 [1895] [LK_DDP/ddp_manager]path check busy on scenario primary_disp [1895] [LK_DDP/ddp_manager]dsi0 is busy [1896] [LK_ENV]get_env scp from area 0 [1896] [SCP] current setting is 1. [1897] mblock_reserve: bddf0000 - bdff0000 from mblock 1 [1898] [PART_LK][get_part] scp1 [SBC] NS-CHIP [1898] [SEC_POLICY] sboot_state = 0x0 [1899] [SEC_POLICY] lock_state(default) = 0x4 [1899] [PART_LK][get_part] scp1 [1899] [PART_LK][get_part] scp1 [1903] ========================================= [1904] [LK_BOOT] scp1 magic number : 0x58881688 [1904] [LK_BOOT] scp1 name : tinysys-loader-CM4_A [1905] [LK_BOOT] scp1 size : 1024 [1905] ========================================= [SBC] NS-CHIP [1908] [SEC_POLICY] sboot_state = 0x0 [1909] [SEC_POLICY] lock_state(default) = 0x4 [1909] [PART_LK][get_part] scp1 [1910] [PART_LK][get_part] scp1 [1911] ========================================= [1912] [LK_BOOT] scp1 magic number : 0x58881688 [1912] [LK_BOOT] scp1 name : tinysys-loader-CM4_A [1913] [LK_BOOT] scp1 size : 1024 [1913] ========================================= [1915] ========================================= [1916] [LK_BOOT] scp1 magic number : 0x58881688 [1916] [LK_BOOT] scp1 name : cert1 [1917] [LK_BOOT] scp1 size : 1685 [1917] ========================================= [1920] ========================================= [1921] [LK_BOOT] scp1 magic number : 0x58881688 [1921] [LK_BOOT] scp1 name : cert2 [1922] [LK_BOOT] scp1 size : 932 [1922] ========================================= [1925] ========================================= [1926] [LK_BOOT] scp1 magic number : 0x58881688 [1926] [LK_BOOT] scp1 name : tinysys-scp-CM4_A [1927] [LK_BOOT] scp1 size : 71728 [1927] ========================================= [1933] LK set emi mpu region protection start:bddf0000 end=bdfeffff region=2 access_permission=b6d169 [1935] [PART_LK][get_part] boot [1935] [PART_LK][get_part] boot [1935] part page addr is 0xb100000 [1938] ============================================================ [1939] [LK_BOOT] Android Partition Name : boot [1940] [LK_BOOT] Android Boot IMG Hdr - Kernel Size : 0x007A955E [1940] [LK_BOOT] Android Boot IMG Hdr - Kernel Address : 0x40080000 [1941] [LK_BOOT] Android Boot IMG Hdr - Rootfs Size : 0x00265A58 [1942] [LK_BOOT] Android Boot IMG Hdr - Rootfs Address : 0x45000000 [1943] [LK_BOOT] Android Boot IMG Hdr - Tags Address : 0x44000000 [1943] [LK_BOOT] Android Boot IMG Hdr - Page Size : 0x00000800 [1944] [LK_BOOT] Android Boot IMG Hdr - Command Line : bootopt=64S3,32N2,64N2 buildvariant=user [1945] ============================================================ [SBC] NS-CHIP [1946] [SEC_POLICY] sboot_state = 0x0 [1947] [SEC_POLICY] lock_state(default) = 0x4 [1947] boot state: green [1947] [PART_LK][get_part] boot [1949] [LK_BOOT] KERNEL partition magic not match [2075] [LK_BOOT] ROOTFS partition magic not match [SBC] NS-CHIP [2076] [SEC_POLICY] sboot_state = 0x0 [2077] [SEC_POLICY] lock_state(default) = 0x4 [2077] [SBC] img vfy disabled [2077] boot state: green [2081] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [2082] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [2083] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [2084] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [2085] [Part_WP]WP(preloader->preloader): Region(1), start_sect(0x0), nr_blk(0x200), type(1) [2089] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [2090] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [SBC] NS-CHIP [2091] [PART_LK][get_part] oemkeystore [2091] [PART_LK][get_part] keystore [2092] [Part_WP]WP(oemkeystore->keystore): Region(8), start_sect(0x40000), nr_blk(0x30000), type(1) [2096] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [2097] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [2097] [mmc_set_user_wp]: card->ext_csd.usr_wp:1 [2098] [mmc_set_write_protect_by_group]: count_wp 12 [2115] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [2116] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [2117] [PART_LK][get_part] seccfg [2117] [PART_LK][get_part] seccfg [2118] [Part_WP]WP(seccfg->seccfg): Region(8), start_sect(0x3c000), nr_blk(0x4000), type(1) [2122] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [2123] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [2123] [mmc_set_user_wp]: card->ext_csd.usr_wp:1 [2124] [mmc_set_write_protect_by_group]: count_wp 1 [2129] EXT_CSD_ERASE_GRP_DEF is Off, wp_size = 8MB, csd.write_prot_grpsz = 15,csd.erase_sctsz = 1024 [2131] [mmc_decode_ext_csd]: mmc_set_wp_size 8MB [2131] write protect Done! [2503] model=MT6797X [2503] cluster-0: 4 core [2504] cluster-1: 4 core [2504] cluster-2: 2 core [2504] Enter load_modem_image v2.0 [2505] ccci_request_mem: ret:8000000, smem_limit:90000000, align:2000000 [2505] mblock_reserve: 88000000 - 90000000 from mblock 1 [2506] request size: 0x08000000, get start address: 0x88000000 [2507] [LK_ENV]get_env opt_ps1_rat from area 1 [2507] [LK_ENV]get_env opt_md1_support from area 1 [2508] [LK_ENV]get_env opt_md3_support from area 1 [2508] [LK_ENV]get_env opt_c2k_lte_mode from area 1 [2509] [LK_ENV]get_env opt_irat_support from area 1 [2510] [LK_ENV]get_env opt_lte_support from area 1 [2510] [LK_ENV]get_env opt_c2k_support from area 1 [2511] using default option setting [2511] default rat:C_LF_LT_W_T_G[0x3f][0x0] [2512] -- MD1 -- [2512] load ptr[md1img] hdr [2512] [PART_LK][get_part] md1img [2516] policy_entry_idx = 12 [SBC] NS-CHIP [2517] [SEC_POLICY] sboot_state = 0x0 [2517] [SEC_POLICY] lock_state(default) = 0x4 [2518] img_auth_required = 0 [2518] mblock_reserve: b2000000 - bc000000 from mblock 2 [2519] request size: 0x0a000000, get start address: 0xb2000000 [2519] [PART_LK][get_part] md1img [2733] ddr_enable_4gb() status=1 [2733] ddr_enable_4GB sta:1 [2733] ---> Map 0x00000000 to 0xb2000000 for MD1(4G) [2734] BANK0_MAP0 value:0xB9B7B5B3 [2734] BANK0_MAP1 value:0xC1BFBDBB [2735] load ptr[md1dsp] hdr [2735] [PART_LK][get_part] md1dsp [2737] policy_entry_idx = 13 [SBC] NS-CHIP [2737] [SEC_POLICY] sboot_state = 0x0 [2738] [SEC_POLICY] lock_state(default) = 0x4 [2738] img_auth_required = 0 [2739] [PART_LK][get_part] md1dsp [2754] load ptr[md1arm7] hdr [2755] [PART_LK][get_part] md1arm7 [2756] policy_entry_idx = 14 [SBC] NS-CHIP [2757] [SEC_POLICY] sboot_state = 0x0 [2757] [SEC_POLICY] lock_state(default) = 0x4 [2758] img_auth_required = 0 [2758] [PART_LK][get_part] md1arm7 [2760] md memory require:0x7000000, reserved:0xa000000 [2760] mblock_resize putback mblock b9000000 size: 3000000 [2771] -- MD3 -- [2771] load ptr[md3img] hdr [2772] [PART_LK][get_part] md3img [2773] policy_entry_idx = 15 [SBC] NS-CHIP [2774] [SEC_POLICY] sboot_state = 0x0 [2774] [SEC_POLICY] lock_state(default) = 0x4 [2775] img_auth_required = 0 [2775] mblock_reserve: bc000000 - bcc00000 from mblock 4 [2776] request size: 0x00c00000, get start address: 0xbc000000 [2777] [PART_LK][get_part] md3img [2828] ddr_enable_4gb() status=1 [2829] ddr_enable_4GB sta:1 [2829] ---> Map 0x00000000 to 0xbc000000 for MD3(4G) [2830] BANK0_MAP0 value:0xC3C1BFBD [2830] BANK0_MAP1 value:0xCBC9C7C5 [2830] md memory require:0xc00000, reserved:0xc00000 [2832] [LK_ENV]get_env apmd1_smem from area 0 [2832] [LK_ENV]get_env md1md3_smem from area 0 [2833] [LK_ENV]get_env apmd3_smem from area 0 [2834] env[apmd1_smem]0. [2834] env[md1md3_smem]0. [2834] env[apmd3_smem]0. [2834] smem_info.base_addr: 88000000 [2835] smem_info.ap_md1_smem_offset: 0 [2835] smem_info.ap_md1_smem_size: 200000 [2836] smem_info.ap_md3_smem_offset: 400000 [2836] smem_info.ap_md3_smem_size: 200000 [2837] smem_info.md1_md3_smem_offset: 200000 [2837] smem_info.md1_md3_smem_size: 200000 [2838] smem_info.total_smem_size: 600000 [2838] ap md1 share mem MPU need configure [2839] md1 md3 share mem MPU need configure [2839] ap md3 share mem MPU need configure [2840] LK set emi mpu region protection start:b2000000 end=b360ffff region=11 access_permission=496db64 [2841] Set MPU:S:0xb2000000 E:0xb360ffff A:<11>[0~7]4-4-5-5-5-5-5-4(U) [2842] LK set emi mpu region protection start:b3610000 end=b545ffff region=12 access_permission=496db44 [2843] Set MPU:S:0xb3610000 E:0xb545ffff A:<12>[0~7]4-0-5-5-5-5-5-4(U) [2844] LK set emi mpu region protection start:b5460000 end=b682ffff region=13 access_permission=16db44 [2845] Set MPU:S:0xb5460000 E:0xb682ffff A:<13>[0~7]4-0-5-5-5-5-5-0(U) [2845] LK set emi mpu region protection start:b6830000 end=b7ffffff region=10 access_permission=416db44 [2847] Set MPU:S:0xb6830000 E:0xb7ffffff A:<10>[0~7]4-0-5-5-5-5-5-0(U) [2847] LK set emi mpu region protection start:b8000000 end=b8ffffff region=14 access_permission=496db44 [2849] Set MPU:S:0xb8000000 E:0xb8ffffff A:<14>[0~7=bc3effff region=16 access_permission=4b45b6c [2850] Set MPU:S:0xbc000000 E:0xbc3effff A:<16>[0~7]4-5-5-5-5-0-5-5(U) [2851] LK set emi mpu region protection start:bc3f0000 end=bcbfffff region=17 access_permission=4b45b6c [2852] Set MPU:S:0xbc3f0000 E:0xbcbfffff A:<17>[0~7]4-5-5-5-5-0-5-5(U) [2853] LK set emi mpu region protection start:88000000 end=881fffff region=7 access_permission=b6db40 [2854] Set MPU:S:0x88000000 E:0x881fffff A:<7>[0~7]0-0-5-5-5-5-5-5(U) [2855] LK set emi mpu region protection start:88200000 end=883fffff region=9 access_permission=b45b40 [2856] Set MPU:S:0x88200000 E:0x883fffff A:<9>[0~7]0-0-5-5-5-0-5-5(U) [2857] LK set emi mpu region protection start:88400000 end=885fffff region=8 access_permission=b45b68 [2858] Set MPU:S:0x88400000 E:0x885fffff A:<8>[0~7]0-5-5-5-5-0-5-5(U) [2859] ddr_enable_4gb() status=1 [2859] ddr_enable_4GB sta:1 [2860] ---> Map 0x40000000 to 0x88000000 for MD1(4G) [2860] BANK4_MAP0 value:0x8F8D8B89 [2861] BANK4_MAP1 value:0x97959391 [2861] before hw remap lock: MD1[0], MD3[0] [2862] before hw remap lock: MD1[1], MD3[0] [2862] ddr_enable_4gb() status=1 [2862] ddr_enable_4GB sta:1 [2863] ---> Map 0x40000000 to 0x88200000 for MD3(4G) [2863] BANK4_MAP0 value:0x8F8D8B89 [2864] BANK4_MAP1 value:0x97959391 [2864] before hw remap lock: MD1[1], MD3[0] [2865] before hw remap lock: MD1[1], MD3[1] [2865] re-size share memory form 8000000 to 600000 [2866] mblock_resize putback mblock 88600000 size: 7a00000 [2866] lk info.lk_info_base_addr: 0x88000000 [2867] lk info.lk_info_size: 0x970 [2867] lk info.lk_info_tag_num: 0x14 [2868] [PROFILE] ------- load_modem_image init cost 364 ms ---- [2869] j:0, mblock[0].rank: 0, size: 0x40000000 [2871] j:1, mblock[0].rank: 0, size: 0x40000000 [2872] j:1, mblock[1].rank: 1, size: 0x8000000 [2875] platform_fdt_scp() [2879] status=okay [2885] target_atag_imix_r:214 [2887] fg_swocv_v buf [0], [0x4608eb48:0x4608eb49:1] [2889] fg_swocv_i buf [0], [0x4608eb48:0x4608eb49:1] [2890] shutdown_time buf [0], [0x4608eb48:0x4608eb49:1] [2891] boot_voltage buf [0], [0x4608eb48:0x4608eb49:1] [2893] Not Support VCORE DVFS [2894] [LK_DDP/RDMA] RDMA0 polling interrupt ret =9999 [2907] [LK_DDP/RDMA] RDMA0 polling interrupt ret =9872 [2926] [LK_DDP/RDMA] RDMA0 polling interrupt ret =9821 [2944] [LK_DDP/RDMA] RDMA0 polling interrupt ret =9821 [2945] mt_disp_get_lcd_time, fps=5398 [2945] videolfb - fb_base = 0xbdff0000 [2946] videolfb - islcmfound = 1 [2946] videolfb - fps = 5398 [2947] videolfb - vram = 33095680 [2947] videolfb - lcmname = aeon_nt36672_fhd_dsi_vdo_x600_xinli [2975] [ccci] modem mem info not support [2976] [ccci] create modem arguments info DT OK [2978] Create PTP DT OK [2979] Create EXTBUCK_FAN53526 DT OK start dump lk masp atag dump sw sbc:22, sw sdl:22 , hw sbc: 0 dump lock_state, 1 dump rid, 2071a2e0, 6b9a5fb6, 187b8992, b88872c2 [2982] create masp atag OK [2982] tee_reserved_mem not supported [2982] [LK] non_secure_sram (0x12a000, 0x6000) [2984] [LK_ENV]get_env usb2jtag from area 0 [2984] [USB2JTAG] current setting is 0. [2985] [LK_ENV]get_env hibboot from area 0 [2985] [LK_ENV]get_env resume from area 0 [2986] resume = NULL [3002] booting linux @ 0x40080000, ramdisk @ 0x45000000 (2513496) [3002] [LEDS]LK: leds_deinit: LEDS off [3006] [LEDS]LK:Cannot find LED node from dts [3009] [LEDS]LK:Cannot find LED node from dts [3013] [LEDS]LK:Cannot find LED node from dts [3016] [LEDS]LK:Cannot find LED node from dts [3020] [LEDS]LK:Cannot find LED node from dts [3023] [LEDS]LK:Cannot find LED node from dts [3027] [LEDS]LK:Cannot find LED node from dts [3027] Cannot not get the LED info from device tree. [3028] [LEDS]LK: red level is 0 [3031] [LEDS]LK:Cannot find LED node from dts [3035] [LEDS]LK:Cannot find LED node from dts [3038] [LEDS]LK:Cannot find LED node from dts [3041] [LEDS]LK:Cannot find LED node from dts [3045] [LEDS]LK:Cannot find LED node from dts [3048] [LEDS]LK:Cannot find LED node from dts [3052] [LEDS]LK:Cannot find LED node from dts [3052] Cannot not get the LED info from device tree. [3053] [LEDS]LK: green level is 0 [3056] [LEDS]LK:Cannot find LED node from dts [3060] [LEDS]LK:Cannot find LED node from dts [3063] [LEDS]LK:Cannot find LED node from dts [3067] [LEDS]LK:Cannot find LED node from dts [3070] [LEDS]LK:Cannot find LED node from dts [3074] [LEDS]LK:Cannot find LED node from dts [3077] [LEDS]LK:Cannot find LED node from dts [3078] Cannot not get the LED info from device tree. [3078] [LEDS]LK: blue level is 0 [3079] [DEVAPC] sec_post_init [3079] [DEVAPC] platform_sec_post_init - SMC call to ATF from LK [3082] DRAM Rank :2 [3083] DRAM Rank[0] Start = 0x40000000, Size = 0x40000000 [3084] DRAM Rank[1] Start = 0x80000000, Size = 0x3ff80000 [3084] mblock[0].start: 0x40000000, size: 0x40000000 [3085] mblock[1].start: 0x80000000, size: 0x8000000 [3086] mblock[2].start: 0x88600000, size: 0x7a00000 [3086] mblock[3].start: 0x90000000, size: 0x22000000 [3087] mblock[4].start: 0xb9000000, size: 0x3000000 [3088] mblock[5].start: 0xbcc00000, size: 0x11f0000 [3089] mblock[6].start: 0xc0000000, size: 0x40000000 [3089] mblock[7].start: 0x100000000, size: 0x40000000 [3090] cmdline: console=tty0 console=ttyMT0,921600n1 root=/dev/ram vmalloc=496M slub_max_order=0 slub_debug=OFZPU androidboot.hardware=mt6797 maxcpus=5 androidboot.verifiedbootstate=green b0 [3095] lk boot time = 2984 ms [3095] lk boot mode = 0 [3096] lk boot reason = power_key [3096] lk finished --> jump to linux kernel 64Bit [3097] [LK]jump to K64 0x40080000 [ATF](0)[3.146080]save kernel info [ATF](0)[3.146460]K64 [ATF](0)[3.146708]pc=0x40080000, r0=0x44000000, r1=0x0 INFO: BL3-1: Preparing for EL3 exit to normal world, Kernel INFO: BL3-1: Next image address = 0x40080000 INFO: BL3-1: Next image spsr = 0x3c9 [ATF](0)[3.148974]el3_exit